# DALLAS JUX

# DS1315 Phantom Time Chip

#### www.maxim-ic.com

### DESCRIPTION

The DS1315 Phantom Time Chip is а combination of a CMOS timekeeper and a nonvolatile memory controller. In the absence of power, an external battery maintains the timekeeping operation and provides power for a CMOS static RAM. The watch keeps track of hundredths of seconds, seconds, minutes, hours, day, date, month, and year information. The last day of the month is automatically adjusted for months with less than 31 days, including leap year correction. The watch operates in one of two formats: a 12-hour mode with an AM/PM indicator or a 24-hour mode. The nonvolatile controller supplies all the necessary support circuitry to convert a CMOS RAM to a nonvolatile memory. The DS1315 can be interfaced with either RAM or ROM without leaving gaps in memory.

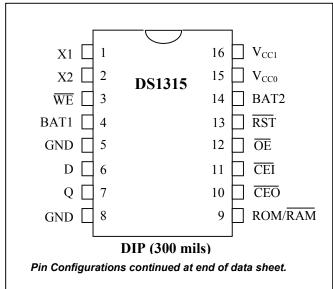

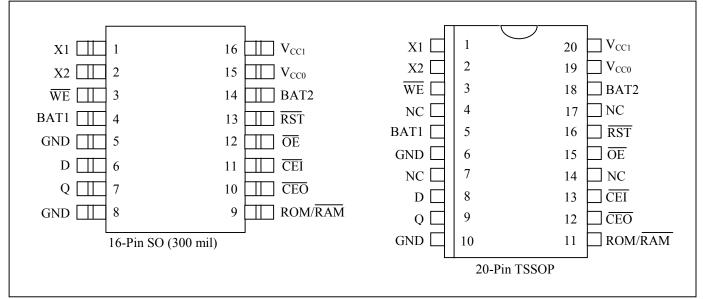

### **PIN CONFIGURATIONS**

### **FEATURES**

- Real-Time Clock Keeps Track of Hundredths of Seconds, Seconds, Minutes, Hours, Days, Date of the Month, Months, and Years

- Adjusts for Months with Fewer than 31 Days

- Automatic Leap Year Correction Valid Up to 2100

- No Address Space Required to Communicate with RTC

- Provides Nonvolatile Controller Functions for Battery Backup of SRAM

- Supports Redundant Battery Attachment for High-Reliability Applications

- Full ±10% V<sub>CC</sub> Operating Range

- +3.3V or +5V Operation

- Industrial (-45°C to +85°C) Operating Temperature Ranges Available

- Drop-In Replacement for DS1215

### **PIN DESCRIPTION**

| X1, X2               | - 32.768 kHz Crystal Connection |

|----------------------|---------------------------------|

| WE                   | - Write Enable                  |

| BAT1                 | - Battery 1 Input               |

| GND                  | - Ground                        |

| D                    | - Data Input                    |

| Q                    | - Data Output                   |

| $ROM/\overline{RAM}$ | - ROM/RAM Mode Select           |

| CEO                  | - Chip Enable Output            |

| CEI                  | - Chip Enable Input             |

| ŌĒ                   | - Output Enable                 |

| RST                  | - Reset                         |

| BAT2                 | - Battery 2 Input               |

| $V_{CC0}$            | - Switched Supply Output        |

| V <sub>CC1</sub>     | - Power Supply Input            |

|                      |                                 |

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: <u>www.maxim-ic.com/errata</u>.

### **ORDERING INFORMATION**

| PART            | TEMP RANGE     | VOLTAGE<br>(V) | PIN-PACKAGE                       | TOP MARK*          |

|-----------------|----------------|----------------|-----------------------------------|--------------------|

| DS1315-33       | 0°C to +70°C   | 3.3            | 16 DIP (300 mils)                 | DS1315 336         |

| DS1315N-33      | -40°C to +85°C | 3.3            | 16 DIP (300 mils)                 | DS1315 336         |

| DS1315-5        | 0°C to +70°C   | 5              | 16 DIP (300 mils)                 | DS1315 56          |

| DS1315N-5       | -40°C to +85°C | 5              | 16 DIP (300 mils)                 | DS1315 56          |

| DS1315E-33      | 0°C to +70°C   | 3.3            | 20 TSSOP (4.4mm)                  | DS1315E XXXX-336   |

| DS1315E-33+     | 0°C to +70°C   | 3.3            | 20 TSSOP (4.4mm)                  | DS1315E XXXX-336 + |

| DS1315EN-33     | -40°C to +85°C | 3.3            | 20 TSSOP (4.4mm)                  | DS1315E XXXX-336   |

| DS1315EN-33+    | -40°C to +85°C | 3.3            | 20 TSSOP (4.4mm)                  | DS1315E XXXX-336 + |

| DS1315EN-33/T&R | -40°C to +85°C | 3.3            | 20 TSSOP/Tape and Reel<br>(4.4mm) | DS1315E XXXX-336   |

| DS1315EN-33+T&R | -40°C to +85°C | 3.3            | 20 TSSOP/Tape and Reel (4.4mm)    | DS1315E XXXX-336 + |

| DS1315E-5       | 0°C to +70°C   | 5              | 20 TSSOP (4.4mm)                  | DS1315E XXXX-56    |

| DS1315E-5+      | 0°C to +70°C   | 5              | 20 TSSOP (4.4mm)                  | DS1315E XXXX-56 +  |

| DS1315EN-5      | -40°C to +85°C | 5              | 20 TSSOP (4.4mm)                  | DS1315E XXXX-56    |

| DS1315EN-5+     | -40°C to +85°C | 5              | 20 TSSOP (4.4mm)                  | DS1315E XXXX-56 +  |

| DS1315EN-5/T&R  | -40°C to +85°C | 5              | 20 TSSOP (4.4mm)                  | DS1315E XXXX-56    |

| DS1315EN-5+T&R  | -40°C to +85°C | 5              | 20 TSSOP (4.4mm)                  | DS1315E XXXX-56 +  |

| DS1315S-33      | 0°C to +70°C   | 3.3            | 16 SO (300 mils)                  | DS1315 336         |

| DS1315S+33      | 0°C to +70°C   | 3.3            | 16 SO (300 mils)                  | DS1315 336 +       |

| DS1315SN-33     | -40°C to +85°C | 3.3            | 16 SO (300 mils)                  | DS1315 336         |

| DS1315SN+33     | -40°C to +85°C | 3.3            | 16 SO (300 mils)                  | DS1315 336 +       |

| DS1315S-5       | 0°C to +70°C   | 5              | 16 SO (300 mils)                  | DS1315 56          |

| DS1315S+5       | 0°C to +70°C   | 5              | 16 SO (300 mils)                  | DS1315 56+         |

| DS1315SN-5      | -40°C to +85°C | 5              | 16 SO (300 mils)                  | DS1315S 56         |

| DS1315SN+5      | -40°C to +85°C | 5              | 16 SO (300 mils)                  | DS1315S 56+        |

| DS1315S-5/T&R   | 0°C to +70°C   | 5              | 16 SO (300 mils)                  | DS1315S 56+        |

| DS1315S+5/T&R   | 0°C to +70°C   | 5              | 16 SO (300 mils)                  | DS1315S 56 +       |

+ Denotes a lead-free/RoHS-compliant device.

\* A "+" symbol located anywhere on the top mark indicates a lead-free device. An "N" located in the bottom right-hand corner of the top of the package denotes an industrial device. "xxxx" can be any combination of characters.

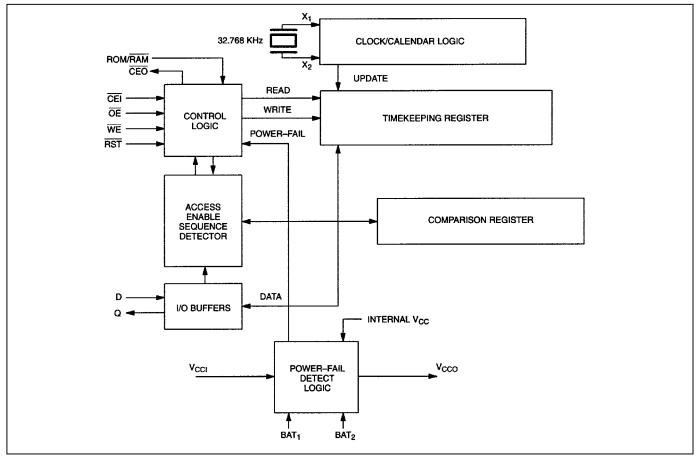

### Figure 1. Block Diagram

### Operation

Communication with the Time Chip is established by pattern recognition of a serial bit stream of 64 bits which must be matched by executing 64 consecutive write cycles containing the proper data on data in (D). All accesses which occur prior to recognition of the 64-bit pattern are directed to memory via the chip enable output pin ( $\overline{\text{CEO}}$ ).

After recognition is established, the next 64 read or write cycles either extract or update data in the Time Chip and  $\overline{\text{CEO}}$  remains high during this time, disabling the connected memory.

Data transfer to and from the timekeeping function is accomplished with a serial bit stream under control of chip enable input ( $\overline{CEI}$ ), output enable ( $\overline{OE}$ ), and write enable ( $\overline{WE}$ ). Initially, a read cycle using the  $\overline{CEI}$  and  $\overline{OE}$  control of the Time Chip starts the pattern recognition sequence by moving pointer to the first bit of the 64-bit comparison register. Next, 64 consecutive write cycles are executed using the  $\overline{CEI}$  and  $\overline{WE}$  control of the Time Chip. These 64 write cycles are used only to gain access to the Time Chip.

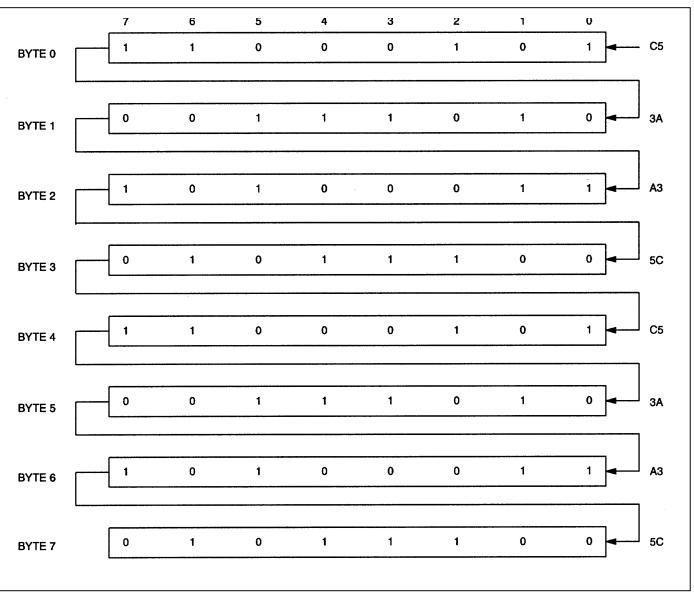

When the first write cycle is executed, it is compared to bit 1 of the 64-bit comparison register. If a match is found, the pointer increments to the next location of the comparison register and awaits the next write cycle. If a match is not found, the pointer does not advance and all subsequent write cycles are ignored. If a read cycle occurs at any time during pattern recognition, the present sequence is aborted and the comparison register pointer is reset. Pattern recognition continues for a total of 64 write cycles as described above until all the bits in the comparison register have been matched. (This bit pattern is shown in Figure 2). With a correct match for 64 bits, the Time Chip is enabled and data transfer to or from the timekeeping registers may proceed. The next 64 cycles will cause the Time Chip to either receive data on D, or transmit data on Q, depending on the level of  $\overrightarrow{OE}$  pin or the  $\overrightarrow{WE}$  pin. Cycles to other locations outside the memory block can be interleaved with  $\overrightarrow{CEI}$  cycles without interrupting the pattern recognition sequence or data transfer sequence to the Time Chip.

A standard 32.768 kHz quartz crystal can be directly connected to the DS1315 via pins 1 and 2 (X1, X2). The crystal selected for use should have a specified load capacitance ( $C_L$ ) of 6 pF. For more information on crystal selection and crystal layout considerations, please consult Application Note 58, "Crystal Considerations with Dallas Real Time Clocks."

**Note:** The pattern recognition in Hex is C5, 3A, A3, 5C, C5, 3A, A3, 5C. The odds of this pattern being accidentally duplicated and causing inadvertent entry to the Phantom Time Chip are less than 1 in 10<sup>19</sup>.

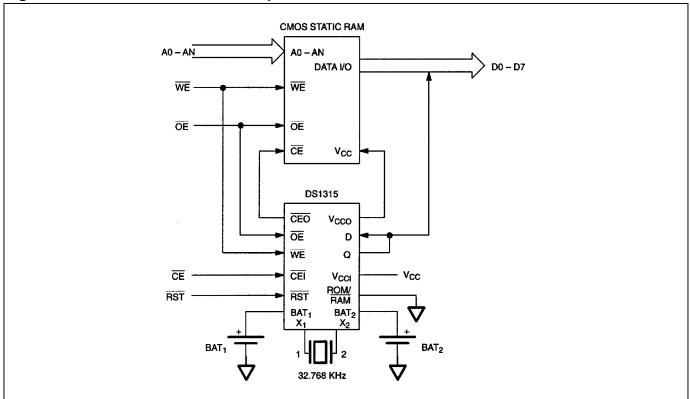

### Nonvolatile Controller Operation

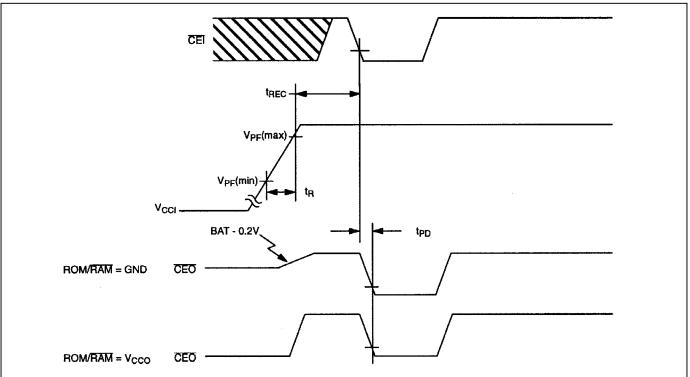

The operation of the nonvolatile controller circuits within the Time Chip is determined by the level of the ROM/ $\overline{\text{RAM}}$  select pin. When ROM/ $\overline{\text{RAM}}$  is connected to ground, the controller is set in the RAM mode and performs the circuit functions required to make CMOS RAM and the timekeeping function nonvolatile. A switch is provided to direct power from the battery inputs or V<sub>CCI</sub> to V<sub>CCO</sub> with a maximum voltage drop of 0.3 volts. The V<sub>CCO</sub> output pin is used to supply uninterrupted power to CMOS SRAM. The DS1315 also performs redundant battery control for high reliability. On power-fail, the battery with the highest voltage is automatically switched to V<sub>CCO</sub>. If only one battery is used in the system, the unused battery input should be connected to ground.

The DS1315 safeguards the Time Chip and RAM data by power-fail detection and write protection. Power-fail detection occurs when  $V_{CCI}$  falls below  $V_{PF}$  which is set by an internal bandgap reference. The DS1315 constantly monitors the  $V_{CCI}$  supply pin. When  $V_{CCI}$  is less than  $V_{PF}$ , power-fail circuitry forces the chip enable output ( $\overline{CEO}$ ) to  $V_{CCI}$  or  $V_{BAT}$ -0.2 volts for external RAM write protection. During nominal supply conditions,  $\overline{CEO}$  will track  $\overline{CEI}$  with a propagation delay. Internally, the DS1315 aborts any data transfer in progress without changing any of the Time Chip registers and prevents future access until  $V_{CCI}$  exceeds  $V_{PF}$ . A typical RAM/Time Chip interface is illustrated in Figure 3.

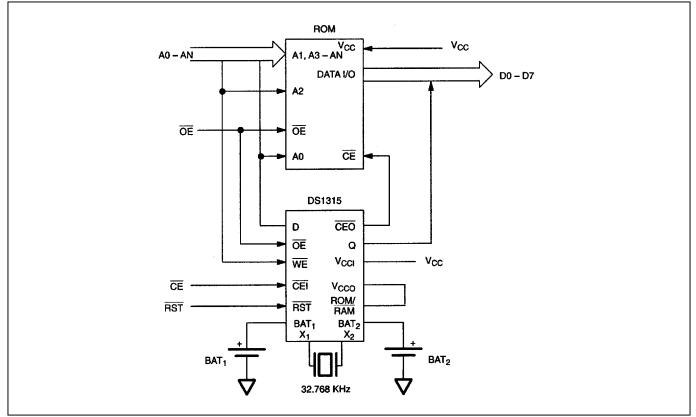

When the ROM/ $\overline{\text{RAM}}$  pin is connected to V<sub>CCO</sub>, the controller is set in the ROM mode. Since ROM is a read-only device that retains data in the absence of power, battery backup and write protection is not required. As a result, the chip enable logic will force  $\overline{\text{CEO}}$  low when power fails. However, the Time Chip does retain the same internal nonvolatility and write protection as described in the RAM mode. A typical ROM/Time Chip interface is illustrated in Figure 4.

#### Figure 3. DS1315-to-RAM/Time Chip Interface

#### Figure 4. ROM/Time Chip Interface

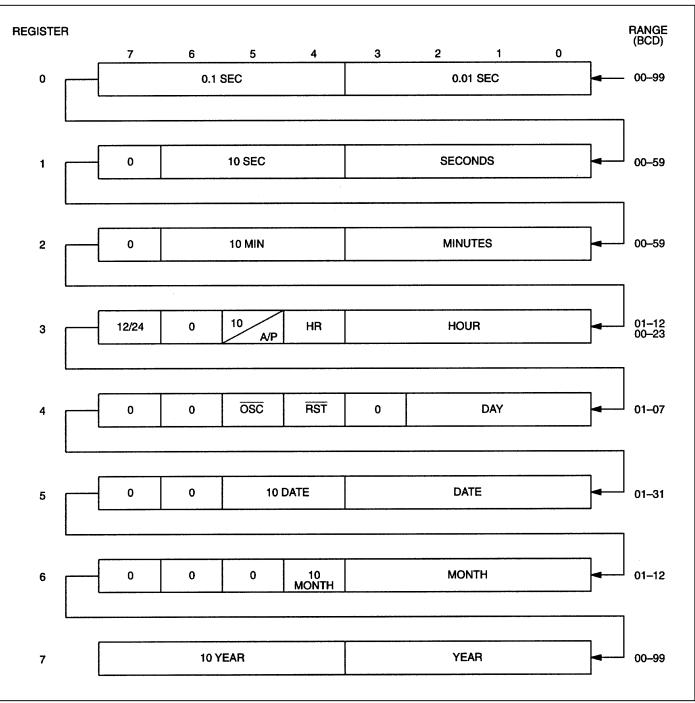

#### **Time Chip Register Information**

Time Chip information is contained in eight registers of 8 bits, each of which is sequentially accessed 1 bit at a time after the 64-bit pattern recognition sequence has been completed. When updating the Time Chip registers, each must be handled in groups of 8 bits. Writing and reading individual bits within a register could produce erroneous results. These read/write registers are defined in Figure 5.

Data contained in the Time Chip registers is in binary coded decimal format (BCD). Reading and writing the registers is always accomplished by stepping though all eight registers, starting with bit 0 of register 0 and ending with bit 7 of register 7.

#### AM–PM/12/24 Mode

Bit 7 of the hours register is defined as the 12- or 24-hour mode select bit. When high, the 12-hour mode is selected. In the 12-hour mode, bit 5 is the AM/PM bit with logic high being PM. In the 24-hour mode, bit 5 is the second 10-hour bit (20-23 hours).

#### **Oscillator and Reset Bits**

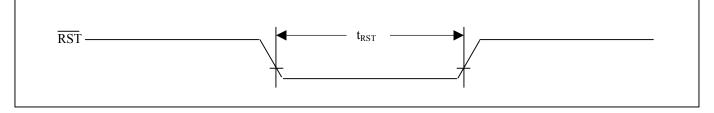

Bits 4 and 5 of the day register are used to control the reset and oscillator functions. Bit 4 controls the reset pin input. When the reset bit is set to logic 1, the reset input pin is ignored. When the reset bit is set to logic 0, a low input on the reset pin will cause the Time Chip to abort data transfer without changing data in the timekeeping registers. Reset operates independently of all other in-puts. Bit 5 controls the oscillator. When set to logic 0, the oscillator turns on and the real time clock/calendar begins to increment.

### Zero Bits

Registers 1, 2, 3, 4, 5, and 6 contain 1 or more bits that will always read logic 0. When writing these locations, either a logic 1 or 0 is acceptable.

### Figure 5. Time Chip Register Definition

### **ABSOLUTE MAXIMUM RATINGS**

Voltage Range on Any Pin Relative to Ground Operating Temperature Range, Commercial Operating Temperature Range, Industrial Storage Temperature Range Soldering Temperature -0.3V to +7.0V 0°C to +70°C -45°C to +85°C -55°C to +125°C See IPC/JEDEC J-STD-020

. .

....

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| RECOMMENDED DC                       | RECOMMENDED DC OPERATING CONDITIONS |      |     |                      |       |       |  |

|--------------------------------------|-------------------------------------|------|-----|----------------------|-------|-------|--|

| PARAMETER SYMBOL MIN TYP MAX         |                                     |      |     |                      | UNITS | NOTES |  |

| Power Supply Voltage 5               | V <sub>CC</sub>                     | 4.5  | 5.0 | 5.5                  | V     | 1     |  |

| Volt Operation                       |                                     |      |     |                      |       |       |  |

| Power Supply Voltage 3.3             | V <sub>CC</sub>                     | 3.0  | 3.3 | 3.6                  | V     | 1     |  |

| Volt Operation                       |                                     |      |     |                      |       |       |  |

| Input Logic 1                        | V <sub>IH</sub>                     | 2.2  |     | V <sub>CC</sub> +0.3 | V     | 1     |  |

| Input Logic 0                        | V <sub>IL</sub>                     | -0.3 |     | +0.6                 | V     | 1     |  |

| Battery Voltage V <sub>BAT1</sub> or | V <sub>BAT1</sub> ,                 | 2.5  |     | 3.7                  | V     |       |  |

| V <sub>BAT2</sub>                    | V <sub>BAT2</sub>                   |      |     |                      |       |       |  |

### **DC OPERATING ELECTRICAL CHARACTERISTICS**

|                                                  |                   |      |                     | (0°C to 70° | $^{\circ}C; V_{CC} =$ | 5.0 ± 10%) |

|--------------------------------------------------|-------------------|------|---------------------|-------------|-----------------------|------------|

| PARAMETER                                        | SYMBOL            | MIN  | ТҮР                 | MAX         | UNITS                 | NOTES      |

| Average V <sub>CC</sub> Power                    | I <sub>CC1</sub>  |      |                     | 5           | mA                    | 6          |

| Supply Current                                   |                   |      |                     |             |                       |            |

| V <sub>CC</sub> Power Supply Current,            | I <sub>CC01</sub> |      |                     | 150         | mA                    | 7          |

| $(V_{CC0} = V_{CCI} - 0.3)$                      |                   |      |                     |             |                       |            |

| TTL Standby Current                              | I <sub>CC2</sub>  |      |                     | 3           | mA                    | 6          |

| $(\overline{\text{CEI}} = V_{\text{IH}})$        |                   |      |                     |             |                       |            |

| CMOS Standby Current                             | I <sub>CC3</sub>  |      |                     | 1           | mA                    | 6          |

| $(\overline{\text{CEI}} = V_{\text{CCI}} - 0.2)$ |                   |      |                     |             |                       |            |

| Input Leakage Current                            | I <sub>IL</sub>   | -1   |                     | +1          | μA                    | 10         |

| (any input)                                      |                   |      |                     |             |                       |            |

| Output Leakage Current                           | I <sub>OL</sub>   | -1   |                     | +1          | μA                    |            |

| (any input)                                      |                   |      |                     |             |                       |            |

| Output Logic 1 Voltage                           | $V_{OH}$          | 2.4  |                     |             | V                     | 2          |

| $(I_{OUT} = -1.0 \text{ mA})$                    |                   |      |                     |             |                       |            |

| Output Logic 0 Voltage                           | $V_{OL}$          |      |                     | 0.4         | V                     | 2          |

| $(I_{OUT} = 4.0 \text{ mA})$                     |                   |      |                     |             |                       |            |

| Power-Fail Trip Point                            | $V_{PF}$          | 4.25 |                     | 4.5         | V                     |            |

| Battery Switch Voltage                           | $V_{SW}$          |      | V <sub>BAT1</sub> , |             |                       | 13         |

|                                                  |                   |      | V <sub>BAT2</sub>   |             |                       |            |

# DC POWER DOWN ELECTRICAL CHARACTERISTICS

|                                                |                   |                       | C to 70°C; $V_{CC}$ < 4.5V) |     |       |       |

|------------------------------------------------|-------------------|-----------------------|-----------------------------|-----|-------|-------|

| PARAMETER                                      | SYMBOL            | MIN                   | TYP                         | MAX | UNITS | NOTES |

| CEO Output Voltage                             | V <sub>CEO</sub>  | V <sub>CCI</sub> -0.2 |                             |     | V     | 8     |

|                                                |                   | or                    |                             |     |       |       |

|                                                |                   | V <sub>BAT1,2</sub>   |                             |     |       |       |

|                                                |                   | -0.2                  |                             |     |       |       |

| V <sub>BAT1</sub> or V <sub>BAT2</sub> Battery | I <sub>BAT</sub>  |                       |                             | 0.5 | μA    | 6     |

| Current                                        |                   |                       |                             |     | -     |       |

| Battery Backup Current                         | I <sub>CCO2</sub> |                       |                             | 10  | μΑ    | 9     |

| @ V <sub>CCO</sub> = V <sub>BAT</sub> -0.2V    |                   |                       |                             |     |       |       |

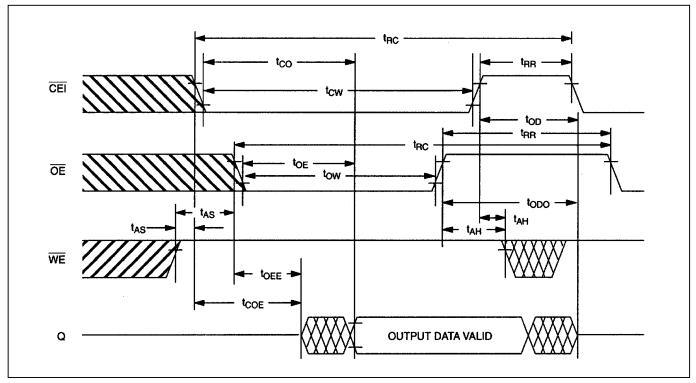

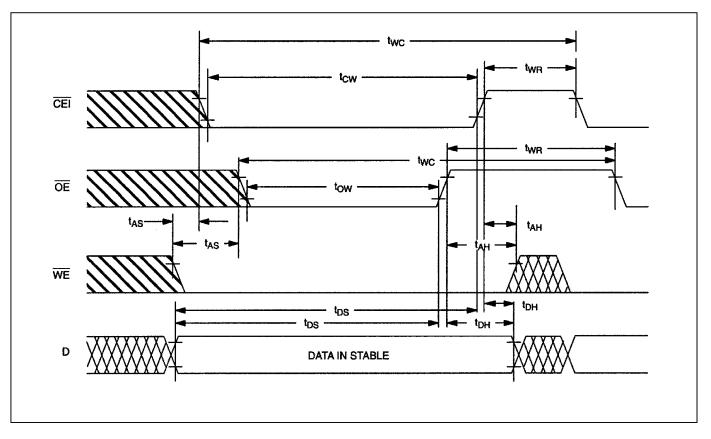

# AC ELECTRICAL OPERATING CHARACTERISTICS

| ROM/RAM = GND        | ROM/RAM = GND    |     |     |     |       | $(0^{\circ}C \text{ to } 70^{\circ}C; V_{CC} = 5.0 \pm 10\%)$ |  |  |  |

|----------------------|------------------|-----|-----|-----|-------|---------------------------------------------------------------|--|--|--|

| PARAMETER            | SYMBOL           | MIN | ТҮР | MAX | UNITS | NOTES                                                         |  |  |  |

| Read Cycle Time      | t <sub>RC</sub>  | 65  |     |     | ns    |                                                               |  |  |  |

| CEI Access Time      | t <sub>CO</sub>  |     |     | 55  | ns    |                                                               |  |  |  |

| OE Access Time       | t <sub>OE</sub>  |     |     | 55  | ns    |                                                               |  |  |  |

| CEI to Output Low Z  | t <sub>COE</sub> | 5   |     |     | ns    |                                                               |  |  |  |

| OE to Output Low Z   | t <sub>OEE</sub> | 5   |     |     | ns    |                                                               |  |  |  |

| CEI to Output High Z | t <sub>OD</sub>  |     |     | 25  | ns    |                                                               |  |  |  |

| OE to Output High Z  | t <sub>ODO</sub> |     |     | 25  | ns    |                                                               |  |  |  |

| Read Recovery        | t <sub>RR</sub>  | 10  |     |     | ns    |                                                               |  |  |  |

| Write Cycle          | t <sub>WC</sub>  | 65  |     |     | ns    |                                                               |  |  |  |

| Write Pulse Width    | t <sub>WP</sub>  | 55  |     |     | ns    |                                                               |  |  |  |

| Write Recovery       | t <sub>WR</sub>  | 10  |     |     | ns    | 4                                                             |  |  |  |

| Data Setup           | t <sub>DS</sub>  | 30  |     |     | ns    | 5                                                             |  |  |  |

| Data Hold Time       | t <sub>DH</sub>  | 0   |     |     | ns    | 5                                                             |  |  |  |

| CEI Pulse Width      | t <sub>CW</sub>  | 55  |     |     | ns    |                                                               |  |  |  |

| OE Pulse Width       | t <sub>OW</sub>  | 55  |     |     | ns    |                                                               |  |  |  |

| RST Pulse Width      | t <sub>RST</sub> | 65  |     |     | ns    |                                                               |  |  |  |

# AC ELECTRICAL OPERATING CHARACTERISTICS

| $ROM/RAM = V_{CCO}$  |                  | $(0^{\circ}C \text{ to } 70^{\circ}C; V_{CC} = 5.0 \pm 10\%)$ |     |     |       |       |

|----------------------|------------------|---------------------------------------------------------------|-----|-----|-------|-------|

| PARAMETER            | SYMBOL           | MIN                                                           | ТҮР | MAX | UNITS | NOTES |

| Read Cycle Time      | t <sub>RC</sub>  | 65                                                            |     |     | ns    |       |

| CEI Access Time      | t <sub>CO</sub>  |                                                               |     | 55  | ns    |       |

| OE Access Time       | t <sub>OE</sub>  |                                                               |     | 55  | ns    |       |

| CEI to Output Low Z  | t <sub>COE</sub> | 5                                                             |     |     | ns    |       |

| OE to Output Low Z   | t <sub>OEE</sub> | 5                                                             |     |     | ns    |       |

| CEI to Output High Z | t <sub>OD</sub>  |                                                               |     | 25  | ns    |       |

| OE to Output High Z  | t <sub>ODO</sub> |                                                               |     | 25  | ns    |       |

| Address Setup Time   | t <sub>AS</sub>  | 5                                                             |     |     | ns    |       |

| Address Hold Time    | t <sub>AH</sub>  | 5                                                             |     |     | ns    |       |

| Read Recovery        | t <sub>RR</sub>  | 10                                                            |     |     | ns    |       |

| Write Cycle          | t <sub>WC</sub>  | 65                                                            |     |     | ns    |       |

| CEI Pulse Width      | t <sub>CW</sub>  | 55                                                            |     |     | ns    |       |

| OE Pulse Width       | t <sub>OW</sub>  | 55                                                            |     |     | ns    |       |

| Write Recovery       | t <sub>WR</sub>  | 10                                                            |     |     | ns    | 4     |

| Data Setup           | t <sub>DS</sub>  | 30                                                            |     |     | ns    | 5     |

| Data Hold Time       | t <sub>DH</sub>  | 0                                                             |     |     | ns    | 5     |

| RST Pulse Width      | t <sub>RST</sub> | 65                                                            |     |     | ns    |       |

### **DC OPERATING ELECTRICAL CHARACTERISTICS**

$(0^{\circ}C \text{ to } 70^{\circ}C; V_{CC} = 3.3 \pm 10\%)$

| $(0 \ C \ 0 \ 7 \ 0 \ C, \ v_{CC} = 3.3 \pm 10$  |                   |     |                     |      |       |       |  |

|--------------------------------------------------|-------------------|-----|---------------------|------|-------|-------|--|

| PARAMETER                                        | SYMBOL            | MIN | ТҮР                 | MAX  | UNITS | NOTES |  |

| Average V <sub>CC</sub> Power                    | I <sub>CC1</sub>  |     |                     | 3    | mA    | 6     |  |

| Supply Current                                   |                   |     |                     |      |       |       |  |

| Average V <sub>CC</sub> Power                    | I <sub>CC01</sub> |     |                     | 100  | mA    | 7     |  |

| Supply Current,                                  |                   |     |                     |      |       |       |  |

| $(V_{CCO} = V_{CCI} - 0.3)$                      |                   |     |                     |      |       |       |  |

| TTL Standby Current                              | I <sub>CC2</sub>  |     |                     | 2    | mA    | 6     |  |

| $(\overline{\text{CEI}} = V_{\text{IH}})$        |                   |     |                     |      |       |       |  |

| CMOS Standby Current                             | I <sub>CC3</sub>  |     |                     | 1    | mA    | 6     |  |

| $(\overline{\text{CEI}} = V_{\text{CCI}} - 0.2)$ |                   |     |                     |      |       |       |  |

| Input Leakage Current                            | I <sub>IL</sub>   | -1  |                     | +1   | μA    |       |  |

| (any input)                                      |                   |     |                     |      |       |       |  |

| Output Leakage Current                           | ILO               | -1  |                     | +1   | μA    |       |  |

| (any input)                                      |                   |     |                     |      |       |       |  |

| Output Logic 1 Voltage                           | V <sub>OH</sub>   | 2.4 |                     |      | V     | 2     |  |

| $(I_{OUT} = 0.4 \text{ mA})$                     |                   |     |                     |      |       |       |  |

| Output Logic 0 Voltage                           | V <sub>OL</sub>   |     |                     | 0.4  | V     | 2     |  |

| $(I_{OUT} = 1.6 \text{ mA})$                     |                   |     |                     |      |       |       |  |

| Power-Fail Trip Point                            | V <sub>PF</sub>   | 2.8 |                     | 2.97 | V     |       |  |

| Battery Switch Voltage                           | $V_{SW}$          |     | V <sub>BAT1</sub> , |      |       | 14    |  |

|                                                  |                   |     | $V_{BAT2}$ ,        |      |       |       |  |

|                                                  |                   |     | or V <sub>PF</sub>  |      |       |       |  |

# DC POWER DOWN ELECTRICAL CHARACTERISTICS

|                                                           |                   | (0°C to 70°C; V <sub>CC</sub> < |     |     |       |       |  |  |  |  |

|-----------------------------------------------------------|-------------------|---------------------------------|-----|-----|-------|-------|--|--|--|--|

| PARAMETER                                                 | SYMBOL            | MIN                             | TYP | MAX | UNITS | NOTES |  |  |  |  |

| CEO Output Voltage                                        | V <sub>CEO</sub>  | V <sub>CCI</sub><br>or          |     |     | V     | 8     |  |  |  |  |

|                                                           |                   | V <sub>BAT1,2</sub><br>-0.2     |     |     |       |       |  |  |  |  |

| V <sub>BAT1</sub> OR V <sub>BAT2</sub><br>Battery Current | I <sub>BAT</sub>  |                                 |     | 0.3 | μΑ    | 6     |  |  |  |  |

| Battery Backup Current<br>$@V_{CCO} = V_{BAT} - 0.2$      | I <sub>CCO2</sub> |                                 |     | 10  | μΑ    | 9     |  |  |  |  |

# AC ELECTRICAL OPERATING CHARACTERISTICS

| ROM/RAM = GND                      |                  |     | $(0^{\circ}C \text{ to } 70^{\circ}C; V_{CC} = 3.3 \pm 10\%)$ |     |       |       |  |  |

|------------------------------------|------------------|-----|---------------------------------------------------------------|-----|-------|-------|--|--|

| PARAMETER                          | SYMBOL           | MIN | TYP                                                           | MAX | UNITS | NOTES |  |  |

| Read Cycle Time                    | t <sub>RC</sub>  | 120 |                                                               |     | ns    |       |  |  |

| CEI Access Time                    | t <sub>CO</sub>  |     |                                                               | 100 | ns    |       |  |  |

| $\overline{\text{OE}}$ Access Time | t <sub>OE</sub>  |     |                                                               | 100 | ns    |       |  |  |

| CEI to Output Low Z                | t <sub>COE</sub> | 5   |                                                               |     | ns    |       |  |  |

| $\overline{OE}$ to Output Low Z    | t <sub>OEE</sub> | 5   |                                                               |     | ns    |       |  |  |

| CEI to Output High Z               | t <sub>OD</sub>  |     |                                                               | 40  | ns    |       |  |  |

| $\overline{OE}$ to Output High Z   | t <sub>ODO</sub> |     |                                                               | 40  | ns    |       |  |  |

| Read Recovery                      | t <sub>RR</sub>  | 20  |                                                               |     | ns    |       |  |  |

| Write Cycle                        | t <sub>WC</sub>  | 120 |                                                               |     | ns    |       |  |  |

| Write Pulse Width                  | t <sub>WP</sub>  | 100 |                                                               |     | ns    |       |  |  |

| Write Recovery                     | t <sub>WR</sub>  | 20  |                                                               |     | ns    | 4     |  |  |

| Data Setup                         | t <sub>DS</sub>  | 45  |                                                               |     | ns    | 5     |  |  |

| Data Hold Time                     | t <sub>DH</sub>  | 0   |                                                               |     | ns    | 5     |  |  |

| CEI Pulse Width                    | t <sub>CW</sub>  | 100 |                                                               |     | ns    |       |  |  |

| $\overline{\text{OE}}$ Pulse Width | t <sub>OW</sub>  | 100 |                                                               |     | ns    |       |  |  |

| RST Pulse Width                    | t <sub>RST</sub> | 120 |                                                               |     | ns    |       |  |  |

# AC ELECTRICAL OPERATING CHARACTERISTICS

| $ROM/RAM = V_{CCO}$  | $OM/RAM = V_{CCO}$ |     |     |     |       | (0°C to 70°C; V <sub>CC</sub> = 3.3 ± 10%) |  |  |  |

|----------------------|--------------------|-----|-----|-----|-------|--------------------------------------------|--|--|--|

| PARAMETER            | SYMBOL             | MIN | ТҮР | MAX | UNITS | NOTES                                      |  |  |  |

| Read Cycle Time      | t <sub>RC</sub>    | 120 |     |     | ns    |                                            |  |  |  |

| CEI Access Time      | t <sub>CO</sub>    |     |     | 100 | ns    |                                            |  |  |  |

| OE Access Time       | t <sub>OE</sub>    |     |     | 100 | ns    |                                            |  |  |  |

| CEI to Output Low Z  | t <sub>COE</sub>   | 5   |     |     | ns    |                                            |  |  |  |

| OE to Output Low Z   | t <sub>OEE</sub>   | 5   |     |     | ns    |                                            |  |  |  |

| CEI to Output High Z | t <sub>OD</sub>    |     |     | 40  | ns    |                                            |  |  |  |

| OE to Output High Z  | t <sub>ODO</sub>   |     |     | 40  | ns    |                                            |  |  |  |

| Address Setup Time   | t <sub>AS</sub>    | 10  |     |     | ns    |                                            |  |  |  |

| Address Hold Time    | t <sub>AH</sub>    | 10  |     |     | ns    |                                            |  |  |  |

| Read Recovery        | t <sub>RR</sub>    | 20  |     |     | ns    |                                            |  |  |  |

| Write Cycle          | t <sub>WC</sub>    | 120 |     |     | ns    |                                            |  |  |  |

| CEI Pulse Width      | t <sub>CW</sub>    | 100 |     |     | ns    |                                            |  |  |  |

| OE Pulse Width       | t <sub>OW</sub>    | 100 |     |     | ns    |                                            |  |  |  |

| Write Recovery       | t <sub>WR</sub>    | 20  |     |     | ns    | 4                                          |  |  |  |

| Data Setup           | t <sub>DS</sub>    | 45  |     |     | ns    | 5                                          |  |  |  |

| Data Hold Time       | t <sub>DH</sub>    | 0   |     |     | ns    | 5                                          |  |  |  |

| RST Pulse Width      | t <sub>RST</sub>   | 120 |     |     | ns    |                                            |  |  |  |

### CAPACITANCE

$(t_{A} = 25^{\circ}C)$

|                    |                  |     |     |     |       | (A = 0 = 0) |

|--------------------|------------------|-----|-----|-----|-------|-------------|

| PARAMETER          | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES       |

| Input Capacitance  | C <sub>IN</sub>  |     |     | 10  | pF    |             |

| Output Capacitance | C <sub>OUT</sub> |     |     | 10  | pF    |             |

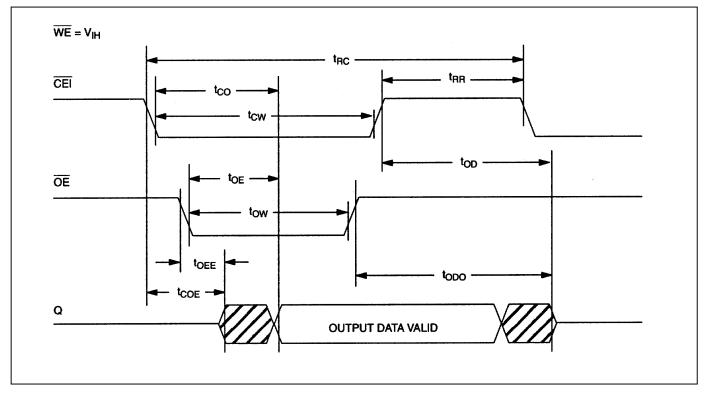

Figure 6. Timing Diagram: Read Cycle to Time Chip ROM/RAM = GND

Figure 8. Timing Diagram: Read Cycle to Time Chip ROM/ $\overline{RAM} = V_{CCO}$

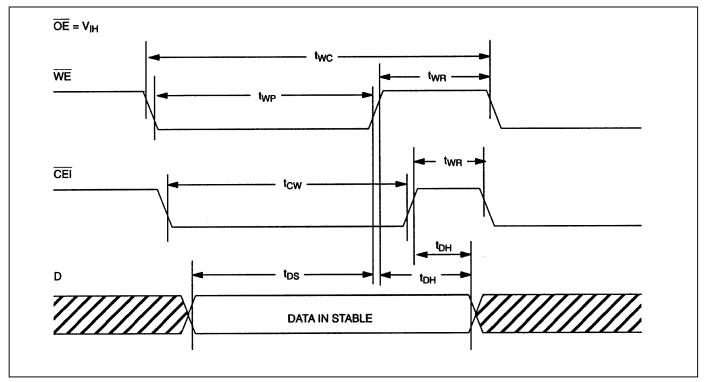

Figure 9. Timing Diagram: Write Cycle to Time Chip ROM/ $\overline{RAM}$  = V<sub>cco</sub>

### Figure 10. Timing Diagram: Reset Pulse

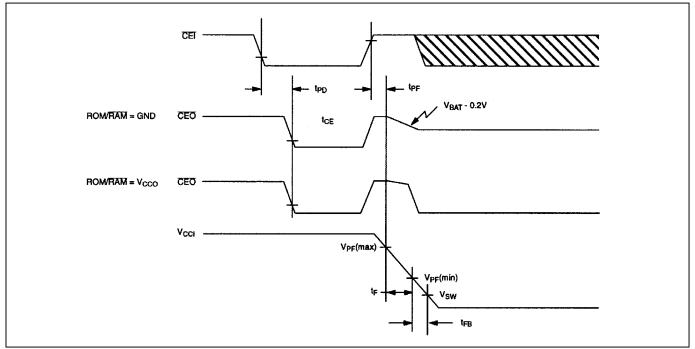

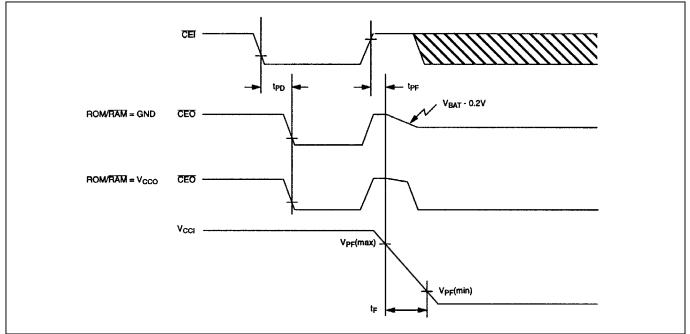

# 5V DEVICE POWER-UP POWER-DOWN CHARACTERISTICS,

| $ROM/RAM = V_{cco} OR GND$     |                  |     |     |     |       | ,<br>(0°C to 70°C) |  |

|--------------------------------|------------------|-----|-----|-----|-------|--------------------|--|

| PARAMETER                      | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES              |  |

| Recovery Time at               | t                | 1.5 |     | 2.5 | mS    | 11                 |  |

| Power-Up                       | t <sub>REC</sub> | 1.3 |     | 2.5 | 1115  | 11                 |  |

| V <sub>CC</sub> Slew Rate      |                  |     |     |     |       |                    |  |

| Power-Down                     | t <sub>F</sub>   | 300 |     |     | μs    | 11                 |  |

| $V_{PF}(max)$ to $V_{PF}(min)$ |                  |     |     |     |       |                    |  |

| V <sub>CC</sub> Slew Rate      |                  |     |     |     |       |                    |  |

| Power-Down                     | $t_{\rm FB}$     | 10  |     |     | μs    | 11                 |  |

| $V_{PF}(min)$ to $V_{SW}$      |                  |     |     |     |       |                    |  |

| V <sub>CC</sub> Slew Rate      |                  |     |     |     |       |                    |  |

| Power-Up                       | t <sub>R</sub>   | 0   |     |     | μs    | 11                 |  |

| $V_{PF}(min)$ to $V_{PF}(max)$ |                  |     |     |     |       |                    |  |

| CEI High to Power-Fail         | t <sub>PF</sub>  |     |     | 0   | μs    | 11                 |  |

| CEI Propagation Delay          | t <sub>PD</sub>  |     |     | 5   | ns    | 2, 3, 11           |  |

### Figure 11. 5V Power-Up Condition

### Figure 12. 5V Power-Down Condition

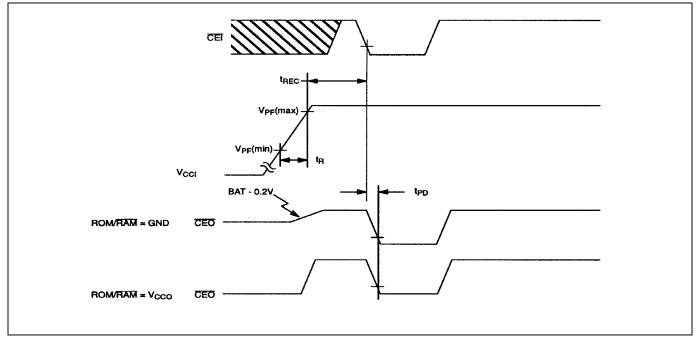

# 3.3V DEVICE POWER-UP POWER-DOWN CHARACTERISTICS,

| $ROM/RAM = V_{cco} OR GND$                                                                |                  |     |     |     |       | (0°C to 70°C) |  |

|-------------------------------------------------------------------------------------------|------------------|-----|-----|-----|-------|---------------|--|

| PARAMETER                                                                                 | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES         |  |

| Recovery Time at<br>Power-Up                                                              | t <sub>REC</sub> | 1.5 |     | 2.5 | ms    | 12            |  |

| V <sub>CC</sub> Slew Rate<br>Power-Down<br>V <sub>PF</sub> (max) to V <sub>PF</sub> (min) | t <sub>F</sub>   | 300 |     |     | μs    | 12            |  |

| $V_{CC}$ Slew Rate<br>Power-Up<br>$V_{PF}(min)$ to $V_{PF}(max)$                          | t <sub>R</sub>   | 0   |     |     | μs    | 12            |  |

| CEI High to Power-Fail                                                                    | t <sub>PF</sub>  | 0   |     |     | μs    | 12            |  |

| CEI Propagation Delay                                                                     | t <sub>PD</sub>  |     |     | 10  | ns    | 2, 3, 11      |  |

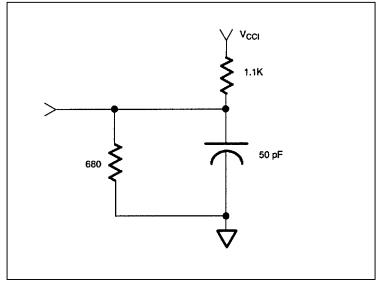

### NOTES:

- 1) All voltages are referenced to ground.

- 2) Measured with load shown in Figure 15.

- 3) Input pulse rise and fall times equal 10 ns.

- 4)  $t_{WR}$  is a function of the latter occurring edge of  $\overline{WE}$  or  $\overline{CE}$  in RAM mode, or  $\overline{OE}$  or  $\overline{CE}$  in ROM mode.

- 5)  $t_{DH}$  and  $t_{DS}$  are functions of the first occurring edge of  $\overline{WE}$  or  $\overline{CE}$  in RAM mode, or  $\overline{OE}$  or  $\overline{CE}$  in ROM mode.

- 6) Measured without RAM connected.

- 7)  $I_{CCO1}$  is the maximum average load current the DS1315 can supply to external memory.

- 8) Applies to  $\overline{\text{CEO}}$  with the ROM/ $\overline{\text{RAM}}$  pin grounded. When the ROM/ $\overline{\text{RAM}}$  pin is connected to V<sub>CCO</sub>,  $\overline{\text{CEO}}$  will go to a low level as V<sub>CCI</sub> falls below V<sub>BAT</sub>.

- 9) I<sub>CCO2</sub> is the maximum average load current that the DS1315 can supply to memory in the battery backup mode.

- 10) Applies to all input pins except  $\overline{RST}$ .  $\overline{RST}$  is pulled internally to V<sub>CCI</sub>.

- 11) See Figures 11 and 12.

- 12) See Figures 13 and 14.

- 13)  $V_{SW}$  is determined by the larger of  $V_{BAT1}$  and  $V_{BAT2}$ .

- 14)  $V_{SW}$  is determined by the smaller of  $V_{BAT1}$ ,  $V_{BAT2}$ , and  $V_{PF}$ .

### Figure 13. 3.3V Power-Up Condition

Figure 14. 3.3V Power-Down Condition

### Figure 15. Output Load

### **PIN CONFIGURATIONS (continued)**

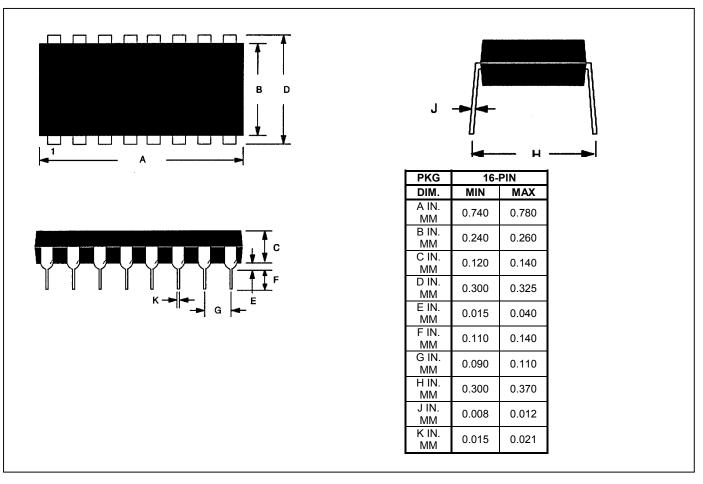

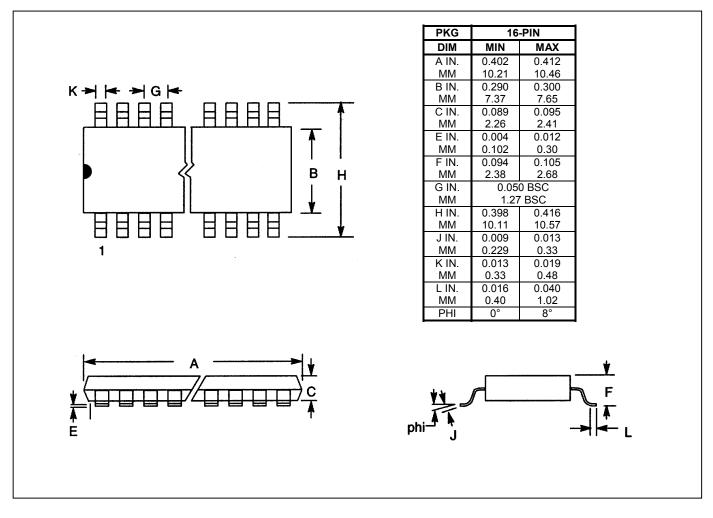

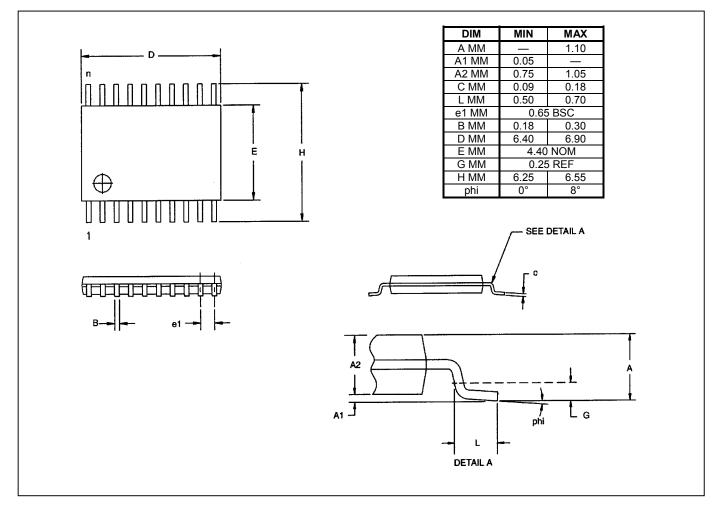

### PACKAGE INFORMATION

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="http://www.maxim-ic.com/DallasPackInfo">www.maxim-ic.com/DallasPackInfo</a>.)

#### **16-PIN DIP**

### 16-PIN SO

#### **16-PIN TSSOP**

Maxim/Dallas Semiconductor cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim/Dallas Semiconductor product. No circuit patent licenses are implied. Maxim/Dallas Semiconductor reserves the right to change the circuitry and specifications without notice at any time. Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 © 2005 Maxim Integrated Products • Printed USA

22 of 22

The Maxim logo is a registered trademark of Maxim Integrated Products, Inc. The Dallas logo is a registered trademark of Dallas Semiconductor Corporation.