Teralane Semiconductor Product Data Sheet

# **TLS8204**

# 102 x 68 Dot Matrix

**STN Segment/Common Driver with Controller**

**Notice:** Specifications and information contained in this Datasheet are subject to change without notice. No part of this Datasheet may be copied or transmitted in any form or by any means, electronic or non-electronic media, for any purpose, without the written permission of Teralane Semiconductor Inc.

**Precautions for light:** Light has the effect of causing the electrons of semiconductor to move and may change the characteristics of semiconductor devices. For this reason, it is necessary to take account of effective protection measures for the packages (such as COB, COG, TCP and COF, etc) causing chip to be exposed to a light environment in order to isolate the projection of light on any part of the chip, including top, bottom and the area around the chip. Follow the precautions below when using this product:

1) During the design stage, it is necessary to notice and confirm the light sensitivity and preventive measures for using IC on substrate (PCB, Glass or Film) or product.

2) Test and inspect the product under an environment free of light source penetration.

3) Confirm that all surfaces around the IC will not be exposed to light source.

# Contents

| INTRODUCTION                                                                                                                                                                                                  | 3  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FEATURES                                                                                                                                                                                                      | 3  |

| BLOCK DIAGRAM                                                                                                                                                                                                 | 4  |

| PIN DESCRIPTION                                                                                                                                                                                               |    |

| FUNCTIONAL DESCRIPTIONS                                                                                                                                                                                       | 9  |

| THE MPU INTERFACE<br>DISPLAY DATA RAM<br>THE OSCILLATOR CIRCUIT<br>THE DISPLAY TIMING CONTROLLER CIRCUIT<br>THE ONE-TIME-PROGRAMMING (OTP) CALIBRATION MODE<br>THE ONER SUPPLY CIRCUITS<br>THE RESET CIRCUITS |    |

| COMMAND TABLE                                                                                                                                                                                                 | 17 |

| COMMAND DESCRIPTION                                                                                                                                                                                           |    |

| INITIALIZATION SEQUENCE OF POWER SUPPLY CIRCUITS                                                                                                                                                              | 27 |

| AC CHARACTERISTICS                                                                                                                                                                                            |    |

| DC CHARACTERISTICS                                                                                                                                                                                            |    |

| ABSOLUTE MAXIMUM RATING                                                                                                                                                                                       |    |

| VLCD CALIBRATION BY OTP                                                                                                                                                                                       |    |

| APPLICATION NOTES                                                                                                                                                                                             |    |

| APPLICATION INFORMATION FOR LCD PANEL (REFERENCE EXAMPLE)<br>Application Information for Pin Connection to MPU (Reference Example)                                                                            |    |

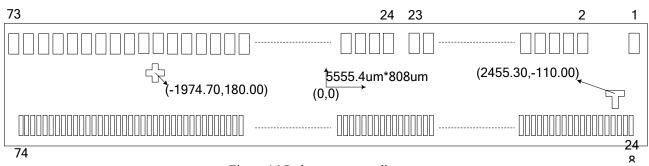

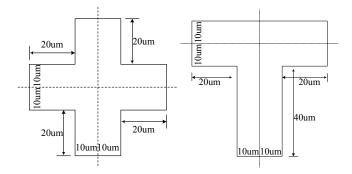

| PAD ARRANGEMENT                                                                                                                                                                                               | 41 |

| PAD CENTER COORDINATES                                                                                                                                                                                        |    |

| REVISION HISTORY                                                                                                                                                                                              | 45 |

# **INTRODUCTION**

The TLS8204 is a low power single-chip driver IC with embedded controller for dot matrix Mono STN LCDs. It contains 170 high voltage driving output circuits and is capable of driving maximum 102 segments, 67 commons with 1 icon LCD panel. In addition to low power COM and SEG drivers, the TLS8204 contains all necessary circuits for high voltage LCD power supply, bias voltage generation, timing generation and dot-matrix display data memory.

The TLS8204 contains an on-chip  $102 \times 68 = 6,936$  bits display data RAM while supporting both parallel and serial MPU interfaces: 8 bits 6800/8080 series parallel interface and 4-line/3-line serial peripheral interface.

Featuring build-in booster and voltage follower capacitors, the TLS8204 requires the fewest peripheral passive components so that the total cost of the display system can be minimized.

### FEATURES

- Driver outputs:

- 102 segments / 67 common + 1 ICON common (1/68 duty)

- 102 segments / 32 common + 1 ICON common (1/33 duty)

- 102 segments / 16 common + 1 ICON common (1/17 duty)

(1/33 duty and 1/17 duty are under partial mode)

- On-chip display data RAM with the capacity of  $102 \times 68 = 6936$  bits

- Multiple MPU interfaces selectable:

- 6800 series parallel interface

- 8080 series parallel interface

- 4-line Serial Peripheral interface (4-line SPI)

- 3-line Serial Peripheral interface (3-line SPI)

- Multiple command functions:

- Display start line set enabling a vertical scroll function

- Segment/Common output mode select

- Display normal/reverse mode, display all points on/off mode

- Partial mode with start COM selectable

- Read-modify-write mode

- LCD bias set, LCD operation voltage regulator ratio set, static indicator set.

- On-chip power supply circuits with booster and voltage follower capacitor built-in

- On-chip LCD driving voltage generator or external power supply selectable

- On-chip DC-DC booster with programmable booster ratio: 2x, 3x, 4x, 5x

- On-chip oscillator for display clock or external clock selectable

- Supports 220-steps of contrast

- Adjustable LCD driving voltage bias ratio: 1/4~1/11

- Thermal gradient = -0.11%/°C

- Power supply voltage:

- VDD = 1.7 3.3V (power for logic)

- VDD2 = 2.4 3.3V (power for analog)

- VLCD = 4.0 10.5 V (LCD driving voltage)

- Package type: COG

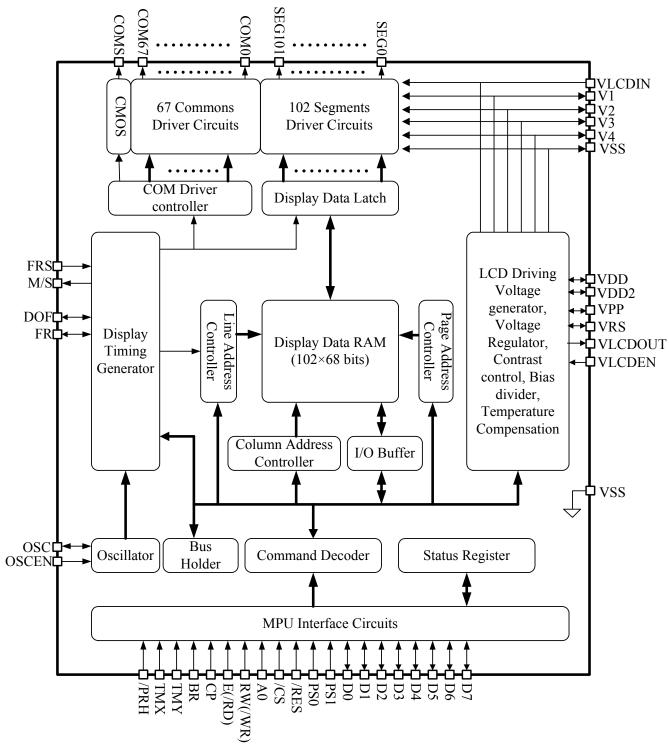

# **BLOCK DIAGRAM**

Figure 1 the block diagram of TLS8204

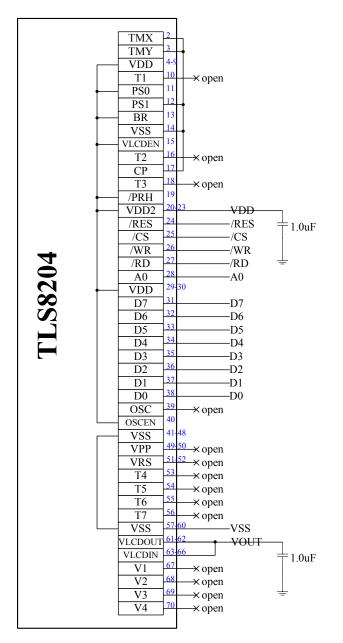

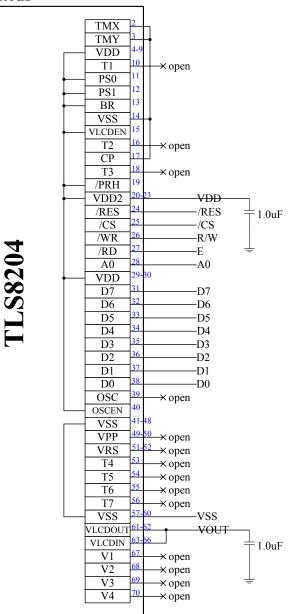

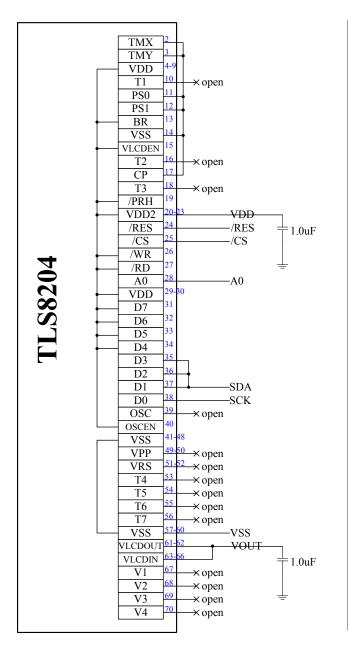

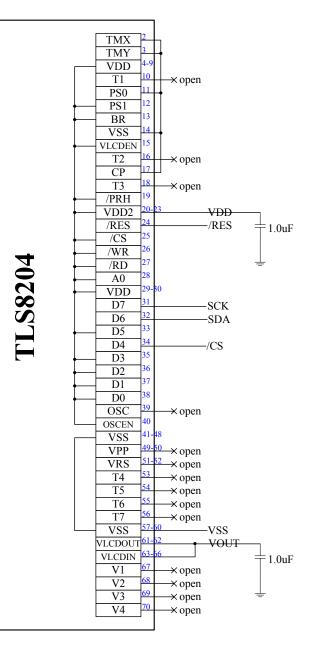

# **PIN DESCRIPTION**

| Name                    | I/O             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | No. of Pins |  |

|-------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

|                         |                 | Power Supply Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |  |

| VDD                     | Power<br>Supply | Power supply for logic circuits. VDD and VDD2 can be connected together.                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8           |  |

| VDD2                    | Power<br>Supply | Power supply for analog circuits. VDD and VDD2 can be connected together.                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4           |  |

| VSS                     | Power<br>Supply | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13          |  |

| VRS                     | Power<br>Supply | Power supply for the internal LCD operation voltage regulator reference circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2           |  |

| VLCDIN                  | Power<br>Supply | This is the LCD operation voltage and power supply for internal HV circuits. When internal voltage booster is used, this pin must be connected to VLCDOUT; when the internal voltage booster is disabled, an external LCD operation voltage should be provided through this pin.                                                                                                                                                                                                                                                        | 4           |  |

| VLCDOUT                 | Power<br>Supply | This is the output of LCD operation voltage VLCD generated by the internal voltage booster. When the internal voltage booster is used, this pin must be connected to VLCDIN; when the internal voltage booster is disabled, this pin should be left open.                                                                                                                                                                                                                                                                               | 2           |  |

| V1,<br>V2,<br>V3,<br>V4 | Power<br>Supply | This is the power supply for the multi-level driving voltage of the LCDs. The voltage supply applied depends on the driving polarity, and the following relationship should be always maintained:<br>$VLCD \ge V1 \ge V2 \ge V3 \ge V4 \ge VSS$<br>These driving voltages can be generated internally. VLCD, V1-V4 are in the relationship of:<br>$V1=(b-1)\times V0/b$ ; $V2=(b-2)\times V0/b$ ; $V3=2\times V0/b$ ; $V4=V0/b$ .<br>Where b is defined as the bias ratio. The bias ratio can be selected from 1/4 to 1/11 by software. | 4           |  |

| VPP                     | Power<br>Supply | OTP programming voltage supply. Left this pin open when normal function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2           |  |

| MPU Interface I/O Pins  |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |  |

| A0                      | Ι               | Thin pin is used to indicate that whether the data bus is data or command.<br>A0 = "H": D7 - D0 are data.<br>A0 = "L": D7 - D0 are command.                                                                                                                                                                                                                                                                                                                                                                                             | 1           |  |

| /RES                    | Ι               | This is the reset pin. When this pin is set to "L", the system registers are set to the initialized status. Refer to the descriptions of Reset Circuits.                                                                                                                                                                                                                                                                                                                                                                                | 1           |  |

| /CS                                                 | Ι   | These are the chip select pins. The chip is set to active when /CS= "H".                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                            | =   | 1 |

|-----------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|

| E<br>(/RD)                                          | Ι   | This pin is the enable indicator (6800 interface mode) or the read<br>operation indicator (8080 interface mode).<br><b>For 6800 series interface applications:</b><br>This is the E pin. Setting E = "H" indicates a write/read operation.<br><b>For 8080 series interface applications:</b><br>This is the /RD pin. Setting /RD = "L" indicates the read operation<br>and the data bus can be read by MPU.<br>When using serial interface, this pin should be fixed to "VDD" or<br>left open. |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                            | 1   | 1 |

| R/W<br>(/WR)                                        | I   | operation inc<br>For 6800 set<br>This is the F<br>(MPU can r<br>indicates the<br>For 8080 set<br>This is the /V<br>and the data                                                                                                                                                                                                                                                                                                                                                                | licator<br>ries int<br>C/W pi<br>ead da<br>write (<br>ries int<br>WR pin<br>bus are                                  | (8080 interface mode).<br><b>cerface applications:</b><br>n. Setting R/W = "H"<br>ta from the data bus)<br>(the TLS8204 chip read<br><b>cerface applications:</b><br>h. Setting /WR = "L" independent of the the terms<br>to be read by the TLS8                                                                                           | dicates the write operation                                                                                                                                                                                                                                                                                                                                                                                                | 1   | 1 |

| D7,<br>D6,<br>D5,<br>D4,<br>D3,<br>D2,<br>D1,<br>D0 | I/O | interface, the<br>serves as SC<br>A0, /CS or D<br>Pin Paname<br>/CS<br>A0<br>D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0<br>Note that left                                                                                                                                                                                                                                                                                                                                                    | e func<br>K, D6<br>04 serve<br>arallel<br>I/F<br>/CS<br>A0<br>D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0<br>ft any | tionality of D7-D0 is<br>or D1, D2, D3 serves as<br>es as /CS.<br>4wire SPI I/F<br>/CS or fixed to "H"<br>A0 or fixed to "H"<br>SCK or fixed to "H"<br>SDA or fixed to "H"<br>A0 or fixed to "H"<br>/CS or fixed to "H"<br>SDA or fixed to "H" | e mode. When using seria<br>very flexible: D7 or D<br>S SDA, A0 or D5 serves a<br>3wire SPI I/F<br>/CS or fixed to "H"<br>Fixed to "H"<br>SDA or fixed to "H"<br>SCK or fixed to "H"<br>SCK or fixed to "H" | ) 5 | 8 |

|          | Γ   | Configuration Pins                                                                                                                                                                                                                                                                                                                                                                         |   |

|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| PS1, PS0 | Ι   | PS0PS1StateLL4 wire-SPI MPU InterfaceLH3 wire-SPI MPU InterfaceHL8080-series parallel MPU interfaceHH6800-series parallel MPU interface                                                                                                                                                                                                                                                    | 2 |

| OSCEN    | I   | <ul><li>When connected to VDD, the internal oscillator will be used for display controller clock;</li><li>When connected to VSS, the internal oscillator is disabled. In this case, an external clock should be input through the OSC pin.</li><li>Please be noted that this pin must not be left open.</li></ul>                                                                          | 1 |

| OSC      | I/O | If the internal oscillator is used (OSCEN pin='H'), this pin is the output of the internal clock;<br>If the internal oscillator is disabled (OSCEN pin = 'L'), this pin is used for clock input.                                                                                                                                                                                           | 1 |

| VLCDEN   | Ι   | When connected to VDD, the internal dc-dc booster is selected;<br>When connected to VSS, the internal dc-dc booster is disabled; an<br>external LCD operating voltage can be input through VLCDIN pin.<br>Please be noted that this pin must not be left open.                                                                                                                             | 1 |

| СР       | Ι   | Set Booster stages default ratio.<br>CP = "L": 4X booster ratio;<br>CP = "H": 5X booster ratio.<br>CP pin set the default value of booster stages after reset; besides, the<br>booster stage can be changed by software command                                                                                                                                                            | 1 |

| BR       | Ι   | Set LCD bias ratio default state.<br>BR = "L": 1/7 bias;<br>BR = "H": 1/9 bias.<br>BR pin set the default value of bias ratio after reset; besides, the bias ratio can be re-configured by software command                                                                                                                                                                                | 1 |

| /PRH     | Ι   | Select LCD operation voltage range.<br>/PRH = "L": The VLCD high range is selected;<br>/PRH = "H". The VLCD low range is selected as initial setting, and<br>the state can be re-configured by the "set VLCD range" command.<br>Please be noted that, when /PRH connected to VSS, the VLCD range<br>can not be re-configured by software.                                                  | 1 |

| ТМХ      | Ι   | This pin selects SEG output direction.<br>TMX = "L": normal direction. (SEG0 $\rightarrow$ SEG101)<br>TMY = "H": reverse direction (SEG101 $\rightarrow$ SEG0)<br>When TMX connected to VSS, the SEG output direction can be<br>re-configured through the "Function set" command. However, when<br>TMX connected to VDD, the SEG output direction can not be<br>re-configured by software. | 1 |

| ТМҮ              | Ι | This pin selects COM s<br>TMY = "L": normal din<br>TMY = "H": reverse di<br>When TMY connected<br>re-configured through t<br>TMY connected to VI<br>re-configured by softwa | rection<br>rection<br>to VS<br>he "F<br>DD, th                  | n.<br>n.<br>SS, the COM sca<br>unction set" com                                                    | mand. However,                                                        | when   | 1   |

|------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------|-----|

|                  | 1 | LCD                                                                                                                                                                         | Driv                                                            | er Pins                                                                                            |                                                                       |        |     |

| SEG0 –<br>SEG101 | 0 | LCD segment driver ou<br>This display data and<br>segment driver.<br>Display M<br>data (inte<br>H H<br>H H<br>L H<br>L H<br>L I<br>Power save mo                            | the M<br>I<br>I<br>I<br>I<br>I                                  |                                                                                                    | •                                                                     | age of | 102 |

| COM0 –<br>COM66  | 0 | LCD column driver out<br>This internal scanning<br>of common driver.<br>Display M<br>data (inte<br>H H<br>H I<br>L H<br>L I<br>Power save mo                                | data a<br><u>1</u><br>rnal)<br><u>1</u><br><u>1</u><br><u>1</u> | and M signal cor<br>Segment driver<br>Normal display<br>VS<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V | output voltage       Reverse display       SS       0       1       4 | oltage | 67  |

| COMS1,<br>COMS2  | 0 | These are the LCD common output pins for the indicator (Icon).<br>Both pins output the same signal. If not use, left these pins open.                                       |                                                                 |                                                                                                    | 2                                                                     |        |     |

|                  |   | ]                                                                                                                                                                           | ſest P                                                          | ins                                                                                                |                                                                       |        |     |

| T1- T7           | 0 | These pins should be le                                                                                                                                                     | ft ope                                                          | n.                                                                                                 |                                                                       |        | 7   |

### **Functional Descriptions**

### The MPU interface

The TLS8204 supports both parallel interface and serial peripheral interface (SPI). Either interface can be selected through the PS1 and PS0 pins. When parallel interface is selected (PS0 = "H"), the D7-D0 is the 8-bit parallel data bus for data transfer. When parallel interface is the selection, both 8080-series (Intel) MPU and 6800-series (Moto) MPU can be connected to the TLS8204 chip. The PS0 pin selects whether it is 6800-series (PS1 = "H") or 8080-series (PS1 = "L") parallel interface. When serial interface is selected (PS0 = "L"), the PS1 pin selects whether it is a 4-line SPI or 3-line SPI. The terminals selected to serve as the serial clock (SCK), serial data (SDA), chip select (/CS) or A0 in 4-line SPI is very flexible so that the restriction on design of system bus connection can be minimized. Table 1 shows the selection of interface type.

|     |     |     |    | Table 1                            |

|-----|-----|-----|----|------------------------------------|

| PS0 | PS1 | /CS | AO | State                              |

| L   | L   | /CS | A0 | 4 wire-SPI MPU Interface           |

| L   | Н   | /CS | *  | 3 wire-SPI MPU Interface           |

| Н   | L   | /CS | A0 | 8080-series parallel MPU interface |

| Н   | Н   | /CS | A0 | 6800-series parallel MPU interface |

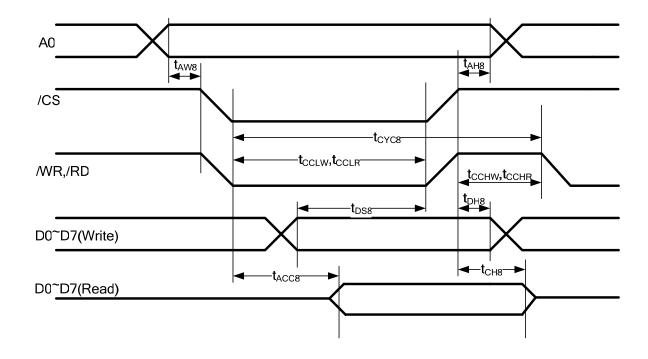

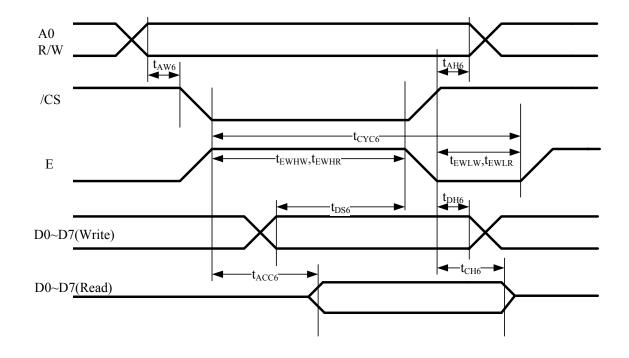

#### The parallel interface

With the parallel interface, the data can be bi-directional transferred between the MPU and the TLS8204 chip through combinational use of D7-D0 data bus and A0, E (/RD), R/W (/WR) terminals. See Table 2.

|     |     |     |    | Table  | 2        |       |             |

|-----|-----|-----|----|--------|----------|-------|-------------|

| PS0 | PS1 | /CS | A0 | E(/RD) | R/W(/WR) | D7~D0 | MPU Bus     |

| Н   | Н   | /CS | A0 | Е      | E/W      | D7~D0 | 6800 series |

| Η   | L   | /CS | A0 | /RD    | /WR      | D7~D0 | 8080 series |

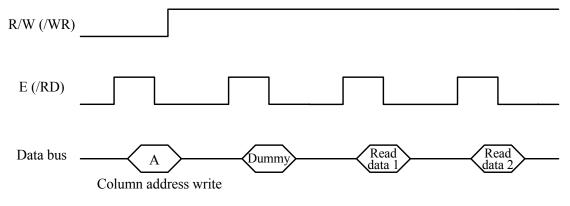

When using the 6800 series interface, R/W = "H" indicates a read operation from the display data RAM or the internal status register and R/W = "L" indicates a write operation to display data RAM or internal command registers depending on the status of A0 pin. The E pin serves as data latch signal when high during chip select is active. Refer to Table 3. In order to realize the pipeline data read from the display data RAM, a dummy read should be inserted before the first actual display data read. This is shown in Figure 3.

Figure 2 Read sequence (6800 interface mode)

When /RD(E) pin is always pulled high for 6800-series interface, it can be used CSB for enable signal. In this case, interface data is latched at the rising edge of CSB and type of data transfer is determined by signals at A0, /WR(R/W) as in case of 6800-series mode.

When 8080-series interface is selected, providing that the chip select is active, the /RD pin serves as data read latch signal when low and the /WR pin serves as data write latch signal when low. Whether the data to be read (or write) from (to) internal display data RAM or internal status register (or command register) is controlled through A0 pin.

Refer to Table 3. Please be noted that a dummy read should also be inserted before the first actual data read.

|        | Table 3     |     |             |     |                              |  |  |

|--------|-------------|-----|-------------|-----|------------------------------|--|--|

| Shared | 6800 Series |     | 8080 Series |     | Function                     |  |  |

| A0     | Е           | R/W | /RD         | /WR | Function                     |  |  |

| 1      | 1           | 1   | 0           | 1   | Reads the display data       |  |  |

| 1      | 1           | 0   | 1           | 0   | Writes the display data      |  |  |

| 0      | 1           | 1   | 0           | 1   | Status read                  |  |  |

| 0      | 1           | 0   | 1           | 0   | Write control data (command) |  |  |

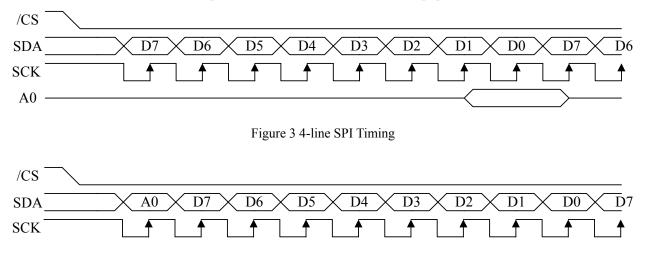

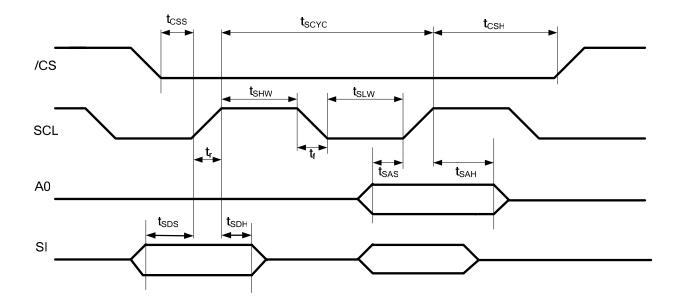

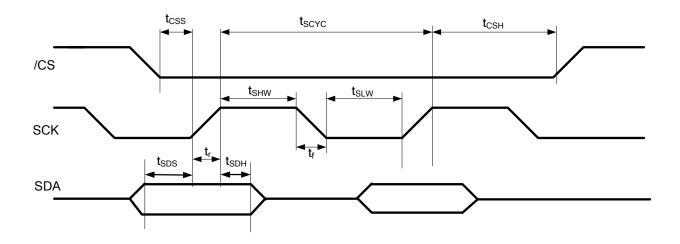

#### The Serial Interface

When the TLS8204 is active (/CS = "L") and PS0 = "L", the serial interface is selected. The display data / command indication may be controlled either through software or the register select pin giving two types of serial interface: 4-line SPI and 3-line SPI. See Table 4.

|     |     |     | Table 4              |            |

|-----|-----|-----|----------------------|------------|

| PS0 | PS1 | /CS | <b>A0</b>            | MPU Bus    |

| L   | L   | /CS | Used                 | 4-line SPI |

| L   | Н   | /CS | Not used, fix to "H" | 3-line SPI |

Moreover, the hardware pins serving as the serial data (SDA), serial clock (SCK), chip select(/CS) and data/command indication (A0, when using 4-line SPI) are chosen from /CS, A0, D7-D0 pins of the TLS8204 chip. The choice can be very flexible. Table 5 shows the mapping relationship between hardware /CS/A0/D7-D0 pins and /CS/A0/SCK/SDA terminals for serial interface.

| Table 5       |                             |                      |  |  |  |  |

|---------------|-----------------------------|----------------------|--|--|--|--|

| Hardware Pins | 4-line SPI                  | 3-line SPI           |  |  |  |  |

| Haruware rins | <b>SPI Terminal Mapping</b> | SPI Terminal Mapping |  |  |  |  |

| /CS           | /CS                         | /CS                  |  |  |  |  |

| A0            | A0                          | Fixed to "VDD"       |  |  |  |  |

| D7            | SCK                         | SCK                  |  |  |  |  |

| D6            | SDA                         | SDA                  |  |  |  |  |

| D5            | A0                          | Fixed to "VDD"       |  |  |  |  |

| D4            | /CS                         | /CS                  |  |  |  |  |

| D3            | SDA                         | SDA                  |  |  |  |  |

| D2            | SDA                         | SDA                  |  |  |  |  |

| D1            | SDA                         | SDA                  |  |  |  |  |

| D0            | SCK                         | SCK                  |  |  |  |  |

For example, if 4-line SPI is selected, any one of D6, D3, D2, D1 hardware pins can be chose as serial data input terminal, they can be connected together or used alone. Please be noted that if any one hardware pin out of /CS, A0, D7 - D0 is not used, it must be fixed to "VDD".

With the SPI interface, the data is read from the serial data input (SDA) at the rising edge of the SPI clock (SCK). The SPI interface circuits treats the serial data in the order of D7, D6 ... D0. Internally, data read from SDA is shifted in the internal 8-bit shift registers and would be processed as an 8-bit parallel data every 8<sup>th</sup> shifting clocks. When the A0 terminal is used, data is display data when A0 is high, and command data when A0 is low. When the A0 is not used, the LCD driver will receive command from MCU by default. If messages on the data pin are data rather than command, MCU should send Data direction command to control the data direction and then one more command to define the number of data bytes will be wrote. After these two continuous commands are sending, the following messages will be data rather than command. Serial data can be read on the rising edge of serial clock going into SCK and processed as 8-bit parallel data on the eighth serial clock. And the DDRAM column address pointer will be increased by one automatically. The next bytes after the display data string are handled as command data. This is referred in Figure 4 and 5.

Note that the above processing is enabled only when the chip select is active. When the chip is not active, the shift

registers and the counter are reset to their initial status. Please also be noted that the read operation is not available with the SPI interface mode. Caution is required on the SCK signal when it comes to line-end reflections and external noise. It is recommend that operation be rechecked on the actual equipment.

Figure 4 3-line SPI Timing

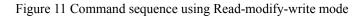

### Display Data RAM

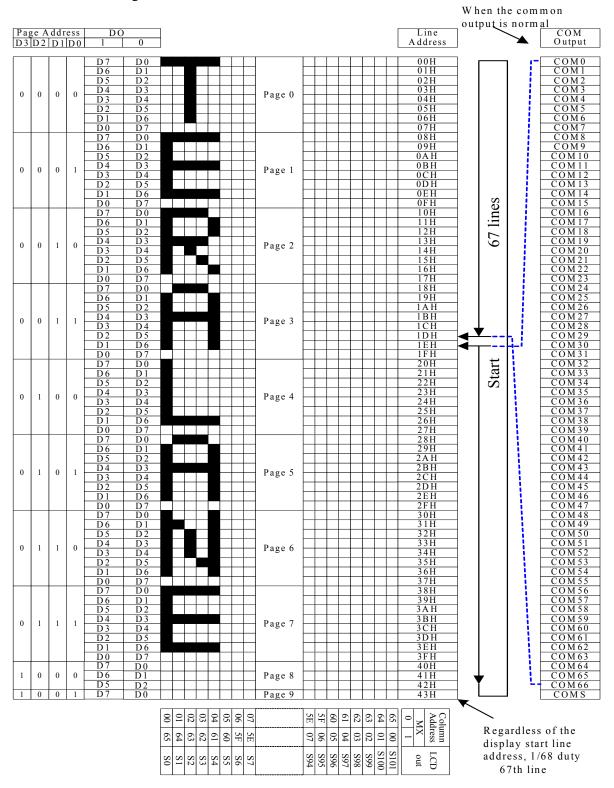

There is a static display data RAM (DDRAM) embedded in the TLS8204 chip supporting  $102 \times 68$  dot-matrix display pattern storage. The internal DDRAM is constructed with  $8pages \times 8bits + 1page \times 3bits + 1 line \times 1bit$  by 102 columns as shown in Figure 6. The DDRAM has a one-to-one correspondence to the dot-matrix display pixel.

Although MPU access and LCD access to the DDRAM could possibly happen simultaneously, the internal DDRAM response to the MPU access through the I/O buffer while process LCD reading request independently, enabling a flicker-free display.

#### The Page Address Circuit

Page address of the internal DDRAM is specified by the Page Address Set command. When the page to access is changed, the page address should be set again. Refer to Figure 6, the  $10^{th}$  page (page address 9) is a special page for icon display, it only contain 1 bit and D0 is used for data access.

#### The Column Addresses Circuit

Column address of the internal DDRAM is specified by the Column Address Set command. For continuously data access, the column address is automatically incremented by 1 with each data read/write command.

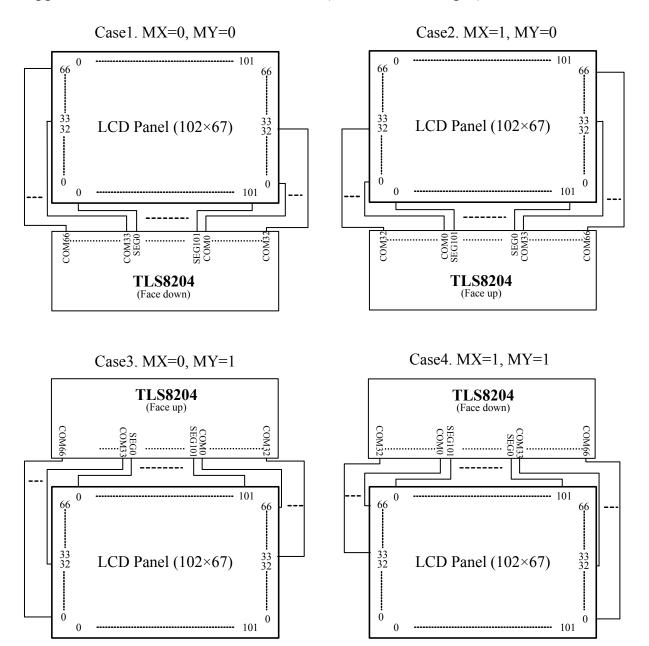

Register MX and MY selection command makes it possible to invert the relationship between the Column Address and the segment outputs. It is necessary to rewrite the display data on built-in RAM after issuing MX select command.

**Segment Output**

|     |        | 5 I                                         |        |

|-----|--------|---------------------------------------------|--------|

| MX  | SEG0   |                                             | SEG101 |

| "0" | seg0   | $\rightarrow$ Segment Address $\rightarrow$ | seg101 |

| "1" | seg101 | $\leftarrow$ Segment Address $\leftarrow$   | seg0   |

#### **Common Output**

| MY  | СОМО                              | COM66                    | COMS |

|-----|-----------------------------------|--------------------------|------|

| "0" | $com0 \rightarrow Common Address$ | $\rightarrow$ com66      | coms |

| "1" | com66←Common Address              | $\leftarrow \text{com0}$ | coms |

#### The Line Address Circuit

For liquid crystal displaying access, the DDRAM is addressed line by line. The content for first line display is determined by the start line address and is specified by the Start Line Address Set command. As shown in Figure 6, by changing the start line address, the display pattern can be swapped. By continuously increment or decrement the start line address, the screen scroll effect can be achieved.

#### **Display Data Latch Circuit**

The line of data to be displayed is temporarily stores in the display data latch. Because the normal/inverse display, display ON/OFF status and display all points ON/OFF is realized within the display data latch, the data within the DDRAM itself do not change.

Figure 5 Display data RAM map (68 COM)

### The Oscillator Circuit

There is an internal oscillator circuit that generates the display clock. The oscillator circuit is only enabled when OSCEN = "H". External display clock is also accepted by the TLS8204 chip. In this case, set OSCEN = "L" to disable the internal oscillator circuit and the external clock is input through the OSC pin.

### The Display Timing Controller Circuit

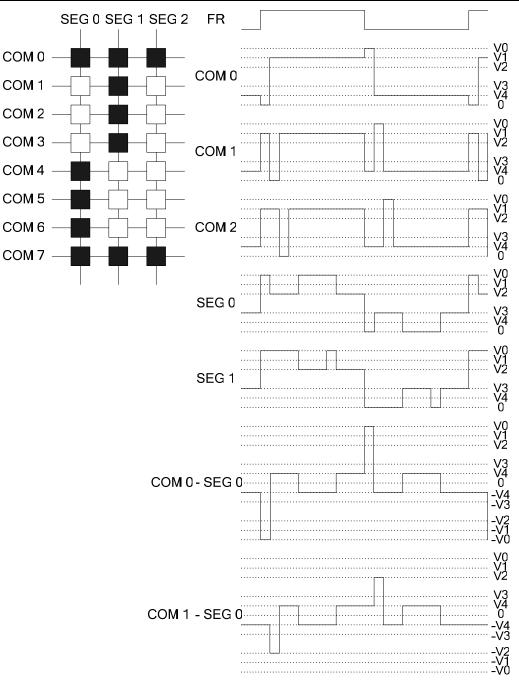

The timing of common scan and its synchronization with segment outputs is controlled by the display timing controller circuits. Based on display clock, the display data is read, latched and sent to the segment driver circuits in synchronous with the common scanning. Frame alternating polarity driving is provided to give an ac drive to liquid crystal displays. The driving polarity is inversed by every frame controlled by the alternating drive signal (FR) generated internally by the timing controller circuits. This is referred in Figure 7.

#### The LCD Driver Circuit

The driver circuits output the driving waveforms required by a liquid crystal display. The waveform is jointly determined by the common scan signal, display pattern and the FR signal. Figure 7 shows an example of the COM and SEG output waveforms.

Figure 6 Example of COM and SEG waveform

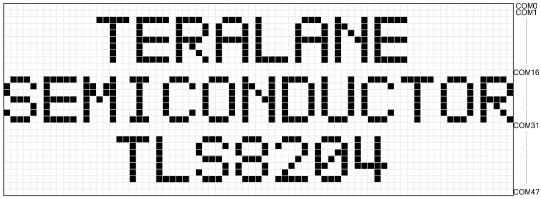

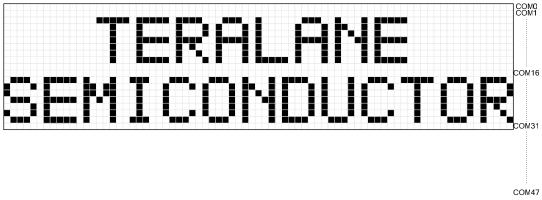

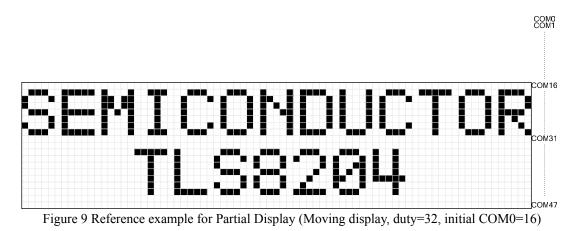

#### The Partial Display on LCD

The TLS8204 incorporates the partial display function on LCD with low-duty driving for saving power consumption. To show the various display duty on LCD, LCD driving duty and bias are programmable by software.

Figure 7 Reference example for Partial Display (full display case)

Figure 8 Reference example for Partial Display (Partial Display duty=32, initial COM0=0)

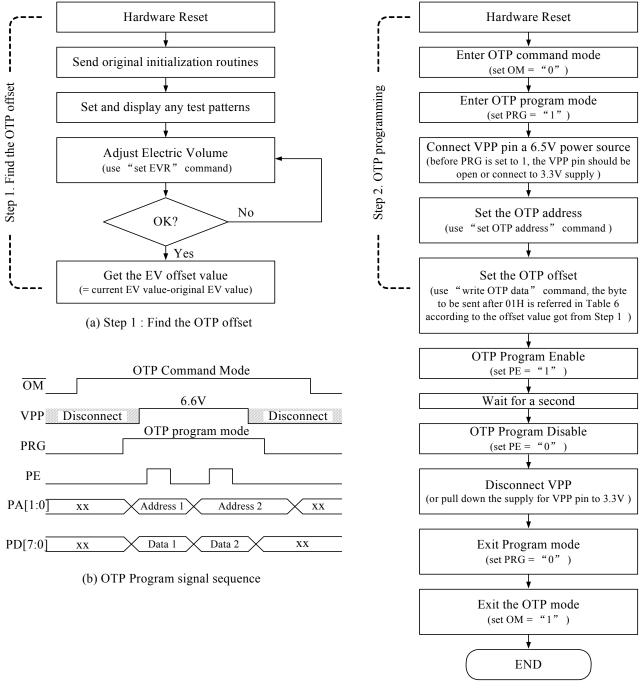

### The One-Time-Programming (OTP) Calibration Mode

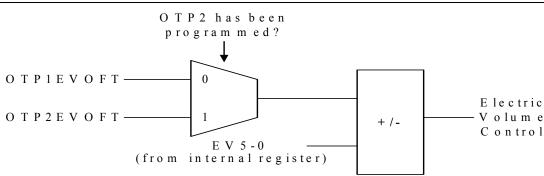

The TLS8204 embeds dual OTP for electric volume offset calibration. OTP is the method to eliminate the variations of LCD module in term of electric volumes so that every LCD module can achieve its best display performance. Figure 11 shows the functional diagram for OTP calibration. By default, the control data would be loaded from internal registers. Once the OTP1 be programmed, the control data would be automatically loaded from OTP1. Once the OTP2 be programmed, the control data would be automatically loaded from OTP1. Once the OTP2 be programmed, the control data would be loaded from OTP2. Please be careful to program OTP1 before OTP2. If OTP2 has been programmed, the control data would be loaded from OTP2, no matter OTP1 has been programmed or not. Please also be noted that if the OTP1/OTP2 has not been programmed, the default value of the OTP1/OTP2 data read out would be all zero.

Figure 10 OTP Calibration for VLCD

### The Power Supply Circuits

The power supply circuits are low-power consumption power supply circuits that generate the voltage levels required for the LCD drivers. They are Booster circuits, voltage regulator circuits, and voltage follower circuits. In TLS8204, the capacitors used for LCD driving voltages generator are built-in so that the least external capacitors are required.

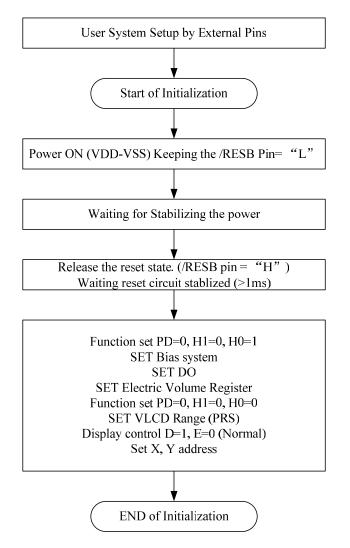

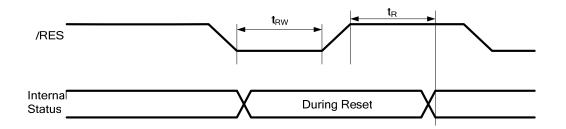

### The Reset Circuits

When the /RES input comes to the "L" level, these LSIs return to the default state. Their default states are as follows:

Page address: 0 Column address: 0 Display control: Display blank COM Scan Direction MY: 0 SEG Select Direction MX: 0 DO=0 FR[2:0]=100 Oscillator: OFF N-line inversion register: 0 (disable) Power down mode (PD=1) Normal command set (H[1:0]=00) Display blank (E=D=0) Address counter X[6:0]=0, Y[3:0]=0 Bias system (BS[2:0]=BR setting) The HV generator is switched off

After power on , RAM data are undefined.

When /RES is "L" or soft reset command is executed, no command except read status can be accepted. With the soft reset command, the reset status appears at D0. After D0 becomes "L", any command can be accepted. /RES must be connected to the reset pin of the MPU and initialize the MPU and this LSI at the same time. The initialization by /RES is essential before used.

# **COMMAND TABLE**

|                     |    |    |                       |                   |                       | H-in                  | deper                 | ndent                 |                       |                   |                              |

|---------------------|----|----|-----------------------|-------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------------------|------------------------------|

| Command             | A0 | WR | <b>D</b> <sub>7</sub> | D <sub>6</sub>    | D <sub>5</sub>        | <b>D</b> <sub>4</sub> | <b>D</b> <sub>3</sub> | <b>D</b> <sub>2</sub> | <b>D</b> <sub>1</sub> | D <sub>0</sub>    | Description                  |

| NOP                 | 0  | 0  | 0                     | 0                 | 0                     | 0                     | 0                     | 0                     | 0                     | 0                 | No operation                 |

| Reserved            | 0  | 0  | 0                     | 0                 | 0                     | 0                     | 0                     | 0                     | 0                     | 1                 | Do not use                   |

| Function Set        | 0  | 0  | 0                     | 0                 | 1                     | MX                    | MY                    | PD                    | H1                    | H0                |                              |

| Read status byte    | 0  | 1  | PD                    | 0                 | 0                     | D                     | Е                     | MX                    | MY                    | DO                |                              |

| Read data           | 1  | 1  | $D_7$                 | $D_6$             | $D_5$                 | $D_4$                 | $D_3$                 | $D_2$                 | <b>D</b> <sub>1</sub> | $D_0$             |                              |

| Write data          | 1  | 0  | $D_7$                 | $D_6$             | $D_5$                 | $D_4$                 | $D_3$                 | $D_2$                 | $D_1$                 | $D_0$             |                              |

| OTP command mode    | 0  | 0  | 0                     | 0                 | 0                     | 0                     | 0                     | 0                     | 1                     | OM                | Enter/exit OTP command mode  |

|                     |    | •  |                       |                   |                       | Н                     | 1H0=                  | 00                    | •                     |                   |                              |

| Command             | A0 | WR | <b>D</b> <sub>7</sub> | D <sub>6</sub>    | D <sub>5</sub>        | <b>D</b> <sub>4</sub> | <b>D</b> <sub>3</sub> | <b>D</b> <sub>2</sub> | <b>D</b> <sub>1</sub> | D <sub>0</sub>    | Description                  |

| Set VLCD range      | 0  | 0  | 0                     | 0                 | 0                     | 0                     | 0                     | 1                     | 0                     | PRS               | VLCD range select            |

| End read modify     | 0  | 0  | 0                     | 0                 | 0                     | 0                     | 0                     | 1                     | 1                     | 0                 | Release read modify write    |

| Read modify write   | 0  | 0  | 0                     | 0                 | 0                     | 0                     | 0                     | 1                     | 1                     | 1                 | RAM address R:+0; W:+1       |

| Display Control     | 0  | 0  | 0                     | 0                 | 0                     | 0                     | 1                     | D                     | 0                     | Е                 | Sets display configuration   |

| Reserved            | 0  | 0  | 0                     | 0                 | 0                     | 1                     | 0                     | 0                     | *                     | *                 | Do not use                   |

| Set Y addr of RAM   | 0  | 0  | 0                     | 1                 | 0                     | 0                     | Y <sub>3</sub>        | $Y_2$                 | $Y_1$                 | $Y_0$             |                              |

| Set X addr of RAM   | 0  | 0  | 1                     | X <sub>6</sub>    | $X_5$                 | $X_4$                 | X <sub>3</sub>        | $X_2$                 | $X_1$                 | $X_0$             |                              |

|                     |    | •  |                       |                   |                       | Н                     | 1H0=                  | 01                    |                       | ,                 |                              |

| Command             | AO | WR | <b>D</b> <sub>7</sub> | D <sub>6</sub>    | D <sub>5</sub>        | <b>D</b> <sub>4</sub> | <b>D</b> <sub>3</sub> | <b>D</b> <sub>2</sub> | <b>D</b> <sub>1</sub> | D <sub>0</sub>    | Description                  |

| Set start line S6   | 0  | 0  | 0                     | 0                 | 0                     | 0                     | 0                     | 1                     | 0                     | S6                | Set S6 for start line        |

| Display Configure   | 0  | 0  | 0                     | 0                 | 0                     | 0                     | 1                     | DO                    | *                     | *                 |                              |

| System bias set     | 0  | 0  | 0                     | 0                 | 0                     | 1                     | 0                     | BS2                   | BS1                   | BS0               |                              |

| Set start line      | 0  | 0  | 0                     | 1                 | S5                    | S4                    | S3                    | S2                    | <b>S</b> 1            | <b>S</b> 0        | Set S5-S0 for start line     |

| Set EVR             | 0  | 0  | 1                     | $\mathrm{EV}_{6}$ | $\mathrm{EV}_5$       | $\mathrm{EV}_4$       | $\mathrm{EV}_3$       | $\mathrm{EV}_2$       | $\mathrm{EV}_1$       | $\mathrm{EV}_{0}$ | Set electric volume register |

|                     |    |    |                       |                   |                       | Η                     | 1H0=                  | 10                    |                       |                   |                              |

| Command             | AO | WR | <b>D</b> <sub>7</sub> | D <sub>6</sub>    | <b>D</b> <sub>5</sub> | <b>D</b> <sub>4</sub> | <b>D</b> <sub>3</sub> | <b>D</b> <sub>2</sub> | <b>D</b> <sub>1</sub> | D <sub>0</sub>    | Description                  |

| Partial screen mode | 0  | 0  | 0                     | 0                 | 0                     | 0                     | 0                     | 1                     | 0                     | PS                | Partial screen enable        |

| Partial screen size | 0  | 0  | 0                     | 0                 | 0                     | 0                     | 1                     | 0                     | 0                     | WS                | Set partial screen size      |

| Display part        | 0  | 0  | 0                     | 0                 | 0                     | 1                     | 0                     | $DP_2$                | $DP_1$                | $DP_0$            | Set display part for PM      |

|                     |    | •  |                       |                   |                       | Н                     | 1H0=                  | 11                    |                       | •                 |                              |

| Command             | A0 | WR | $\mathbf{D}_7$        | D <sub>6</sub>    | D <sub>5</sub>        | <b>D</b> <sub>4</sub> | <b>D</b> <sub>3</sub> | <b>D</b> <sub>2</sub> | <b>D</b> <sub>1</sub> | D <sub>0</sub>    | Description                  |

| RESET               | 0  | 0  | 0                     | 0                 | 0                     | 0                     | 0                     | 0                     | 1                     | 1                 | Software reset               |

| Frame frequency     | 0  | 0  | 0                     | 0                 | 0                     | 0                     | 1                     | $FR_2$                | $FR_1$                | $FR_0$            | Frame rate control           |

| Set Booster         | 0  | 0  | 1                     | 0                 | 0                     | 1                     | $BE_1$                | $BE_0 \\$             | $PC_1$                | $PC_0$            | Efficiency & stage           |

| N line inversion    | 0  | 0  | 0                     | 1                 | 0                     | $NL_4$                | $NL_3$                | $NL_2$                | $NL_1$                | $NL_0$            | Sets N line inversion        |

| Read register/OTP   | 0  | 0  | 1                     | 0                 | 0                     | 0                     | 1                     | 0                     | 0                     | RO                | Select read register or OTP  |

|                     |    |    | H-inc                 | lepen             | dent                  | , OM                  | =0 (C                 | TP c                  | omm                   | and r             | node)                        |

| Command             | A0 | WR | $\mathbf{D}_7$        | D <sub>6</sub>    | D <sub>5</sub>        | <b>D</b> <sub>4</sub> | <b>D</b> <sub>3</sub> | <b>D</b> <sub>2</sub> | <b>D</b> <sub>1</sub> | D <sub>0</sub>    | Description                  |

| Write OTP data      | 0  | 0  | 0                     | 0                 | 0                     | 0                     | 0                     | 0                     | 0                     | 1                 | Write the programming data   |

|                     | 0  | 0  | $D_7$                 | $D_6$             | $D_5$                 | $D_4$                 | D <sub>3</sub>        | D <sub>2</sub>        | <b>D</b> <sub>1</sub> | $D_0$             |                              |

| OTP program mode    | 0  | 0  | 1                     | 1                 | 0                     | 0                     | 0                     | 1                     | 0                     | PRG               | Enter/Exit OTP program mode  |

| OTP program enable  | 0  | 0  | 1                     | 1                 | 0                     | 0                     | 0                     | 1                     | 1                     | PE                | OTP program enable           |

| Set OTP address     | 0  | 0  | 1                     | 1                 | 0                     | 0                     | 1                     | 0                     | $PA_1$                | $PA_0$            | Set OTP programming address  |

# **COMMAND DESCRIPTION**

The commands of TLS8204 are divided into several groups defined by H[1:0] register. A command can be correctly executed only when the H register is currently points to the corresponding H1H0 value which the command is belonged to. But for those commands that are H-independent, they can be correctly executed no matter what value the H register points to. Moreover, the OTP programming commands are only enabled at OTP command mode defined by OM register. Once OM=0, these OTP programming commands are valid independent of H register.

### H independent Groups

#### **Function Set**

| A0 | /WR(R/W) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----------|----|----|----|----|----|----|----|----|

| 0  | 0        | 0  | 0  | 1  | MX | MY | PD | H1 | H0 |

| Register | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| МХ       | SEG bi-directional selection<br>MX=0: normal direction (SEG0 → SEG101)<br>MX=1: reverse direction (SEG101 → SEG0)                                                                                                                                                                                                                                                                                                                       |

| МҮ       | COM bi-directional selection<br>MY=0: normal direction (COM0 $\rightarrow$ COM66)<br>MY=1: reverse direction (COM66 $\rightarrow$ COM0)                                                                                                                                                                                                                                                                                                 |

| PD       | <ul> <li>PD=0: chip is active with normal function.</li> <li>PD=1: chip is step into power down mode.</li> <li>When the power down mode is stepped in: <ul> <li>All LCD outputs at V<sub>ss</sub> (display off)</li> <li>Bias generator and VLCD generator is turned off</li> <li>Internal oscillator is turned off (external clock possible)</li> <li>RAM contents not cleared</li> <li>RAM data can be written</li> </ul> </li> </ul> |

| H1 H0    | H1,H0 are used to select different command group.<br>Follow the command table.                                                                                                                                                                                                                                                                                                                                                          |

Note that the MX and MY register can be set through both this function set command and hardware configuration pin TMX and TMY. The MX and MY control registers is determined by:

MX (control register) = TMX (hardware pin) **OR** MX (software set) MY (control register) = TMY (hardware pin) **OR** MY (software set)

For both MX and MY control registers, "0" specifies normal direction and "1" specifies reverse direction. That is, if the TMX pin is fixed to "H", then the SEG output direction is always from SEG101 to SEG0 (reverse direction) no matter what is sent to MX by command; if the TMX pin is fixed to "L", then the SEG output direction is determined by the software set value to MX, "0" for normal and "1" for reverse. It is very similar for MY control register, when TMY hardware pin is fixed to "H", the common scan direction is reverse and can not be re-configured by software, and when it is fixed to "L", whether the common scan direction is normal or reverse is determined by the command set.

#### Read status byte

| A0 | /WR(R/W) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |

|----|----------|----|----|----|----|----|----|----|----|

| 0  | 1        | PD | 0  | 0  | D  | Е  | MX | MY | DO |

The explanation for each flag is referred in command description sections for "Function set", "Display control" and "Display configure" commands.

#### Read data

8-bit data of Display Data from the RAM location specified by the column address and page address can be read to the microprocessor.

| A0 | /WR(R/W) | <b>D7</b> | D6 | D5 | D4   | D3   | D2 | D1 | D0 |

|----|----------|-----------|----|----|------|------|----|----|----|

| 1  | 1        |           |    |    | Read | data |    |    |    |

#### Write data

8-bit data of Display Data from the microprocessor can be written to the RAM location specified by the column address and page address. The column address is increased by 1 automatically so that the microprocessor can continuously write data to the addressed page. During auto-increment, the column address wraps to 0 after the last column is written.

| AO | /WR(R/W) | <b>D7</b> | D6         | D5 | D4 | D3 | D2 | D1 | D0 |  |  |

|----|----------|-----------|------------|----|----|----|----|----|----|--|--|

| 1  | 0        |           | Write data |    |    |    |    |    |    |  |  |

#### NOP

| A0 | /WR(R/W) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |

|----|----------|----|----|----|----|----|----|----|----|

| 0  | 0        | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

This command takes on operation.

#### **OTP command mode**

| ſ | A0 | /WR(R/W) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |

|---|----|----------|----|----|----|----|----|----|----|----|

| ſ | 0  | 0        | 0  | 0  | 0  | 0  | 0  | 0  | 1  | OM |

OM=0: OTP command mode. The OTP programming commands are become valid only during this mode. OM=1: OTP command mode release.

### H[1:0]=[0:0] Groups

#### Set VLCD range

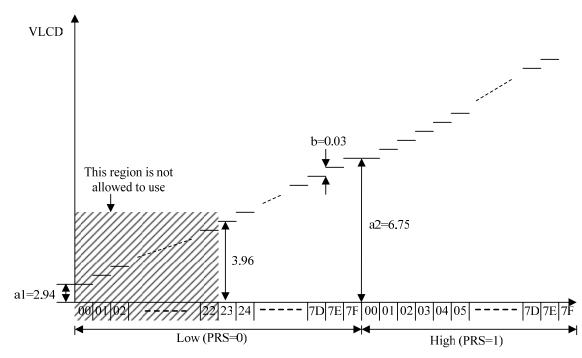

This command sets the high or low range of VLCD. Refer to Figure 14.

| A0 | /WR(R/W) | <b>D</b> 7 | D6 | D5 | D4 | D3 | D2 | D1 | DO  |

|----|----------|------------|----|----|----|----|----|----|-----|

| 0  | 0        | 0          | 0  | 0  | 0  | 0  | 1  | 0  | PRS |

PRS=0: VLCD range is set to low;

PRS=1: VLCD range is set to high.

The VLCD range can be set through both this command and hardware configuration pin /PRH. When /PRH is fixed to "L", the VLCD high range is fixed, and the set VLCD range command can not change this status. When /PRH is fixed to "H", the VLCD range is determined by this command.

#### **Display control**

| A0 | /WR(R/W) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----------|----|----|----|----|----|----|----|----|

| 0  | 0        | 0  | 0  | 0  | 0  | 1  | D  | 0  | Е  |

The bits D and E select the display mode.

| Regis | sters | Description             |

|-------|-------|-------------------------|

| D     | Е     | Description             |

| 0     | 0     | Display off             |

| 1     | 0     | Normal display          |

| 0     | 1     | All display segments on |

| 1     | 1     | Inverse video mode      |

#### Set Y address of RAM

Y [3:0] defines the Y address vector address of the display RAM.

| A0 | /WR(R/W) | D7 | D6 | D5 | D4 | D3             | D2             | D1    | D0             |

|----|----------|----|----|----|----|----------------|----------------|-------|----------------|

| 0  | 0        | 0  | 1  | 0  | 0  | Y <sub>3</sub> | Y <sub>2</sub> | $Y_1$ | Y <sub>0</sub> |

| Y <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Y <sub>0</sub> | Content              |

|----------------|----------------|----------------|----------------|----------------------|

| 0              | 0              | 0              | 0              | Page 0 (display RAM) |

| 0              | 0              | 0              | 1              | Page 1 (display RAM) |

| 0              | 0              | 1              | 0              | Page 2 (display RAM) |

| 0              | 0              | 1              | 1              | Page 3 (display RAM) |

| 0              | 1              | 0              | 0              | Page 4 (display RAM) |

| 0              | 1              | 0              | 1              | Page 5 (display RAM) |

| 0              | 1              | 1              | 0              | Page 6 (display RAM) |

| 0              | 1              | 1              | 1              | Page 7 (display RAM) |

| 1              | 0              | 0              | 0              | Page 8 (display RAM) |

| 1              | 0              | 0              | 1              | Page 9 (display RAM) |

#### Set X address of RAM

The X address points to the columns. The range of X is  $0 \cdots 101$ .

| A0 | /WR(R/W) | D7 | D6    | D5    | D4    | D3 | D2    | D1    | D0    |

|----|----------|----|-------|-------|-------|----|-------|-------|-------|

| 0  | 0        | 1  | $X_6$ | $X_5$ | $X_4$ | X3 | $X_2$ | $X_1$ | $X_0$ |

The X[6:0] varies from 0 to 101 correspond to the column address from 0 to 101.

#### **Read modify write**

| A0 | /WR(R/W) | <b>D</b> 7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |

|----|----------|------------|----|----|----|----|----|----|----|

| 0  | 0        | 0          | 0  | 0  | 0  | 0  | 1  | 1  | 1  |

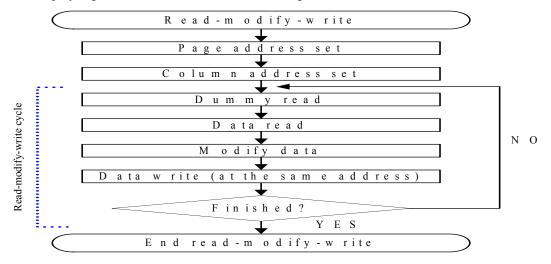

This command is used paired with the "End read modify" command. Once this command has been input, the display data read command does not change the column and row address, but only the display data write command increments (+1) the address. This mode is maintained until the End read modify command is input. When the End read modify command is entered, the address returns to the address it was at when the read modify write command was entered. This function makes it possible to reduce the load on the MPU when there are repeating data changes in a specified display region, such as when there is a blanking cursor.

Note that other commands beside Display data read/write commands can also be used even in Read-modify-write mode.

#### End read modify

| A0 | /WR(R/W) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----------|----|----|----|----|----|----|----|----|

| 0  | 0        | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  |

This command releases the read/modify/write mode, and returns the column and row address to the address it was at when the mode was entered.

### H[1:0]=[0:1] Groups

#### **Display configuration**

This command sets the data byte oriental in the display data RAM. As shown in Figure 13, the MSB is on the top side or the bottom side depends on the setting of the DO register.

| A0 | /WR(R/W) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----------|----|----|----|----|----|----|----|----|

| 0  | 0        | 0  | 0  | 0  | 0  | 1  | DO | *  | *  |

"\*" refers to don't care bit.

Figure 12 RAM data structure depends on the DO setting

#### System bias set

The command sets the system bias ratio.

| A0 | /WR(R/W) | D7              | D6 | D5              | D4 | D3   | D2              | D1             | DO     |

|----|----------|-----------------|----|-----------------|----|------|-----------------|----------------|--------|

| 0  | 0        | 0               | 0  | 0               | 1  | 0    | BS <sub>2</sub> | $BS_1$         | $BS_0$ |

| BS | 52       | BS <sub>1</sub> |    | BS <sub>0</sub> |    | Bias | Re              | Recommended D  |        |

| 0  | )        | 0               |    | 0               |    | 11   |                 | 1/100          |        |

| 0  | )        | 0               |    | 1               | 10 |      |                 | 1/81           |        |

| 0  | )        | 1               |    | 0               |    | 9    |                 | 1/65, 1/       | 68     |

| 0  | )        | 1               |    | 1               |    | 8    |                 | 1/49           |        |

| 1  |          | 0               |    | 0               |    | 7    |                 | 1/40, 1/36     |        |

| 1  |          | 0               |    | 1               |    | 6    |                 | 1/24           |        |

| 1  |          | 1               |    | 0               |    | 5    |                 | 1/18, 1/16     |        |

| 1  |          | 1               |    | 1               |    | 4    |                 | 1/10, 1/9, 1/8 |        |

The TLS8204 chip give a R-R-nR-R-R bias system, where R = VLCD-V1 = V1-V2 = V3-V4 = V4-VSS and

nR=V2-V3. The bias ratio is calculated as 1/b=1/(n+4).

#### Set start line

This command sets the line address of display data RAM as the initial display line. The RAM display data is displayed at the top of row (COM0) of LCD panel. The  $S_6$  must be defined first, and then defined  $S_5$  to  $S_0$ .

| A0 | /WR(R/W) | <b>D7</b> | D6 | D5 | D4 | D3 | D2 | D1 | DO    |

|----|----------|-----------|----|----|----|----|----|----|-------|

| 0  | 0        | 0         | 0  | 0  | 0  | 0  | 1  | 0  | $S_6$ |

|    |          |           |    |    |    |    |    |    |       |

|    |          |           |    |    |    |    |    |    |       |

| A0 | /WR(R/W) | D7        | D6 | D5 | D4 | D3 | D2 | D1 | D0    |

The  $S_{6^{-0}}$  sets the start line address. Because the line address of internal data RAM is addressed from 0-66 for MPU accessible display area, a value of  $S_{6^{-0}}$  larger than 66 is not allowed.

#### Set EVR

This command sets the Electric Volume Register. The level of VLCD (=V0) voltage is determined by the Electric Volume Register. Different level of VLCD gives different contrast at human vision from liquid crystal display.

| A0 | /WR(R/W) | D7 | D6     | D5     | D4              | D3     | D2              | D1     | DO              |

|----|----------|----|--------|--------|-----------------|--------|-----------------|--------|-----------------|

| 0  | 0        | 1  | $EV_6$ | $EV_5$ | $\mathrm{EV}_4$ | $EV_3$ | EV <sub>2</sub> | $EV_1$ | $\mathrm{EV}_0$ |

In TLS8204, steps of contrast are divided into two parts: low VLCD range and high VLCD range. Which range is set to active depends on the setting of the PRS register that can be set by the set VLCD range command. The VLCD voltage can be programmed through software according to the formula as below:

$$VLCD = a + EV \times b$$

The parameters of "a" and "b" are explained in the table below.

| Symbol | Value        | Unit |

|--------|--------------|------|

| al     | 2.94 (PRS=0) | V    |

| a2     | 6.75 (PRS=1) | V    |

| b      | 0.03         | V    |

Figure 13 sketch of Electric Volume steps

The maximum VLCD level also depends on the VDD2 voltage and the display load current. For those situations that the higher VLCD voltage and larger load current are required, higher booster level and higher VDD2 level are also required; for those situations that relatively lower VLCD voltage is satisfied with the display performance, both the booster level and the VDD2 can be relatively lower so that the power consumption can be reduced.

When /PRH hardware pin is fixed to "H", two overlapping VLCD ranges are selectable via the set VLCD range command. For the low VLCD range (PRS=0) "a"=a1 and for the high VLCD range (PRS=1) "a"=a2 with steps equal to "b" in both ranges. During normal or partial display, the EV[6:0] can be programmed in the range of 00H-7FH while PRS=1 and in the range of 23H-7FH while PRS=0, giving a 220 steps of programmable contrast levels as shown in Figure 14.

When /PRH hardware pin is fixed to "L", only high range VLCD is valid.

#### Please be noted that:

\* When PRS and EV[6:0] is set to all zero, the internal booster circuits is turned off, no matter the /PRH pin is fixed to high or low.

\* When low VLCD range is selected (PRS=0), the EV[6:0] $\geq$  23 should be kept. While PRS=0, if the EV[6:0] smaller than 23 is set (except for the case EV[6:0]=0), the VLCD will keep the volume determined by EV[6:0]=23.

\* For the normal or partial display mode application, the VLCD level must be operated in the range of 4V to 9.5V. Situations that VLCD is lower than 4V or higher than 9.5V are only for testing.

### H[1:0]=[1:0] Groups

#### Partial screen mode

| A0 | /WR(R/W) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |

|----|----------|----|----|----|----|----|----|----|----|

| 0  | 0        | 0  | 0  | 0  | 0  | 0  | 1  | 0  | PS |

| Register | Description                                                                                              |

|----------|----------------------------------------------------------------------------------------------------------|

|          | PS=0: Full display mode with MUX 1:68                                                                    |

| PS       | PS=1: Partial screen mode, the partial screen size of MUX 1:17 or 1:33 is determined by the WS register. |

When enter Partial screen mode, COMS also works. The DDRAM position of COMS is at page9.

#### Partial screen size

| A0 | /WR(R/W) | <b>D7</b> | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----------|-----------|----|----|----|----|----|----|----|

| 0  | 0        | 0         | 0  | 0  | 0  | 1  | 0  | 0  | WS |

| Register | Description                                                |

|----------|------------------------------------------------------------|

| WS       | WS=0: Partial screen mode with MUX 1:17(16 Common + COMS)  |

| VV 5     | PS=1: Partial screen mode with MUX 1:33( 32 Common + COMS) |

#### **Display Part**

| I | A0 | /WR(R/W) | D7 | D6 | D5 | D4 | D3 | D2              | D1     | D0              |

|---|----|----------|----|----|----|----|----|-----------------|--------|-----------------|

|   | 0  | 0        | 0  | 0  | 0  | 1  | 0  | DP <sub>2</sub> | $DP_1$ | DP <sub>0</sub> |

The range of display common and DDRAM depends on the "WS" register . For example , if WS=1 and DP[2:0]=001, then display common is common 8 to common 39 and the DDRAM position is page 1 to page4 and COMS is at page9.

Moreover, the bottom of DP[2:0] is common 66, when the range is over common66, there will be no more common output to display. Thus, please set the DP[2:0] properly so that the last common address would not exceed the bottom address (common 66).

| Registers        |                                   | Status               |                                                                               | Descri               | iption                |

|------------------|-----------------------------------|----------------------|-------------------------------------------------------------------------------|----------------------|-----------------------|

| Registers        |                                   | Status               |                                                                               | Display common       | <b>DDRAM</b> position |

|                  | 0                                 | 0                    | 0         1           1         0           1         1           0         0 | Start from common 0  | Start from page 0     |

|                  | 0                                 | 0                    | 1                                                                             | Start from common 8  | Start from page 1     |

|                  | 0                                 | 1                    | 0                                                                             | Start from common 16 | Start from page 2     |

| $DP_2 DP_1 DP_0$ | 0                                 | 1                    | 1                                                                             | Start from common 24 | Start from page 3     |

|                  | 1                                 | 0                    | 0                                                                             | Start from common 32 | Start from page 4     |

|                  | 1                                 | 0                    | 1                                                                             | Start from common 40 | Start from page 5     |

|                  | 1                                 | 1                    | 0                                                                             | Start from common 48 | Start from page 6     |

|                  | 1     1     0       1     1     1 | Start from common 56 | Start from page 7                                                             |                      |                       |

### H[1:0]=[1:1] Groups

#### Soft Reset

This command resets initial display line, column address, page address, and common output status select to their initial status .This command cannot initialize the LCD power supply, which is initialized by the RESB pin.

| ſ | A0 | /WR(R/W) | <b>D7</b> | D6 | D5 | D4 | D3 | D2 | D1 | D0 |